The Translation Lookahead Buffer (TLB) is a cache for paging addresses.

When TLB is filled up, older addresses are overwritten. Just like CPU cache, the replacement policy is a potentially complex operation, but a simple and reasonable heuristic is to remove the least recently used entry (LRU).

With LRU, starting from state:adding

valid linear physical

----- ------ --------

> 1 00003 00005

1 00007 00009

1 00009 00001

1 0000B 000030000D -> 0000A would give: valid linear physical

----- ------ --------

1 0000D 0000A

> 1 00007 00009

1 00009 00001

1 0000B 00003In

v4.2, look under arch/x86/:include/asm/pgtable*include/asm/page*mm/pgtable*mm/page*

There seems to be no structs defined to represent the pages, only macros:

include/asm/page_types.h is specially interesting. Excerpt:#define _PAGE_BIT_PRESENT 0 /* is present */

#define _PAGE_BIT_RW 1 /* writeable */

#define _PAGE_BIT_USER 2 /* userspace addressable */

#define _PAGE_BIT_PWT 3 /* page write through */Two level address translation to make OS emulation more efficient.

Peter Cordes mentions that some architectures like MIPS leave paging almost completely in the hands of software: a TLB miss runs an OS-supplied function to walk the page tables, and insert the new mapping into the TLB. In such architectures, the OS can use whatever data structure it wants.

Information about ARM paging can be found at: cirosantilli.com/linux-kernel-module-cheat#arm-paging

Free:

- rutgers-pxk-416 chapter "Memory management: lecture notes"

Intel is known to have created customized chips for very large clients.

This is mentioned e.g. at: www.theregister.com/2021/03/23/google_to_build_server_socs/Those chips are then used only in large scale server deployments of those very large clients. Google is one of them most likely, given their penchant for Google custom hardware.

Intel is known to do custom-ish cuts of Xeons for big customers.

TODO better sources.

The bad:

- Clunky UI

- circuit diagram doesn't show any state??

- github.com/ekondis/mixbench GPL

- github.com/ProjectPhysX/OpenCL-Benchmark custom non-commercial, non-military license

- 2020: Traininum in 2020, e.g. techcrunch.com/2020/12/01/aws-launches-trainium-its-new-custom-ml-training-chip/

- 2018: AWS Inferentia, mentioned at en.wikipedia.org/wiki/Annapurna_Labs

Pinned article: Introduction to the OurBigBook Project

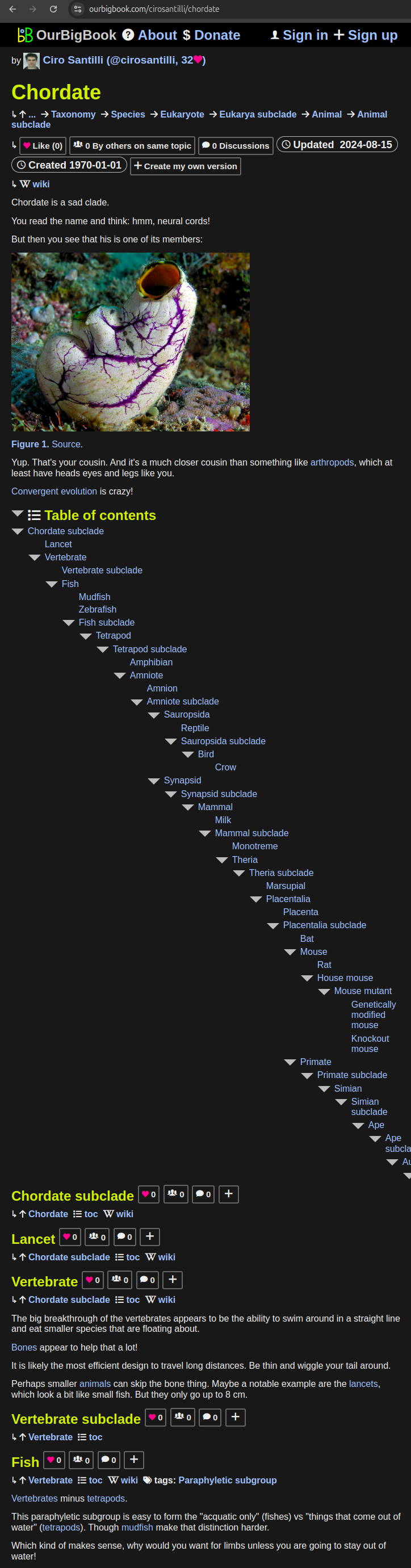

Welcome to the OurBigBook Project! Our goal is to create the perfect publishing platform for STEM subjects, and get university-level students to write the best free STEM tutorials ever.

Everyone is welcome to create an account and play with the site: ourbigbook.com/go/register. We belive that students themselves can write amazing tutorials, but teachers are welcome too. You can write about anything you want, it doesn't have to be STEM or even educational. Silly test content is very welcome and you won't be penalized in any way. Just keep it legal!

Intro to OurBigBook

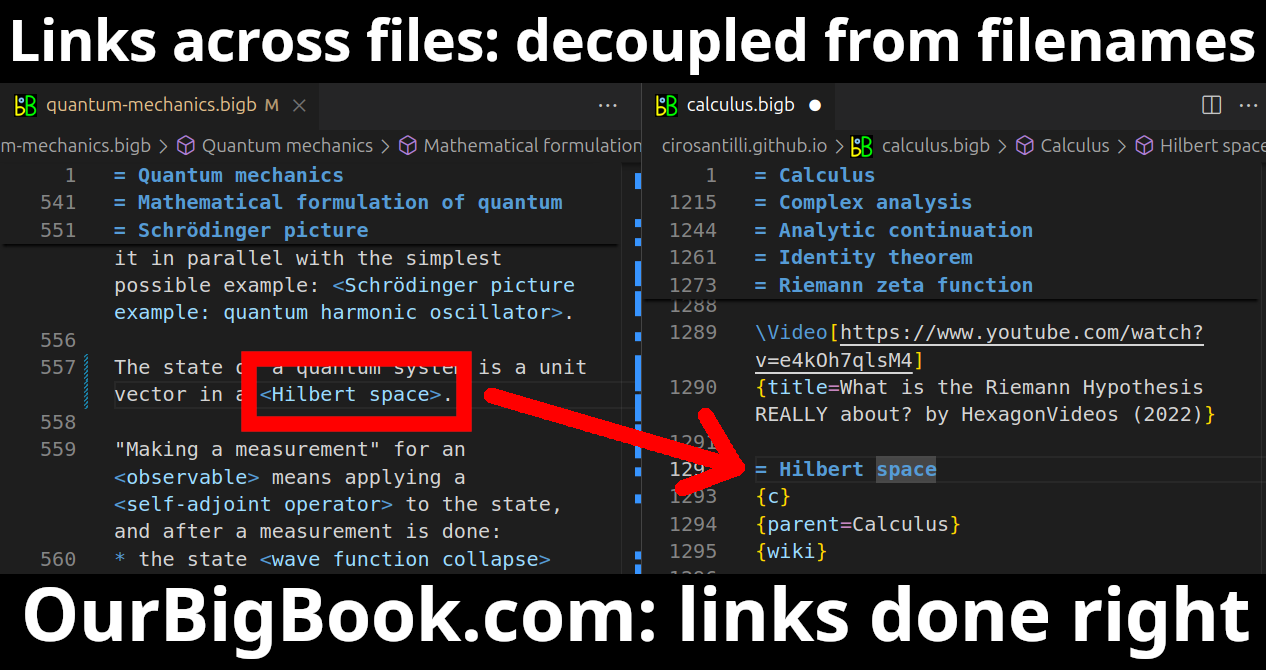

. Source. We have two killer features:

- topics: topics group articles by different users with the same title, e.g. here is the topic for the "Fundamental Theorem of Calculus" ourbigbook.com/go/topic/fundamental-theorem-of-calculusArticles of different users are sorted by upvote within each article page. This feature is a bit like:

- a Wikipedia where each user can have their own version of each article

- a Q&A website like Stack Overflow, where multiple people can give their views on a given topic, and the best ones are sorted by upvote. Except you don't need to wait for someone to ask first, and any topic goes, no matter how narrow or broad

This feature makes it possible for readers to find better explanations of any topic created by other writers. And it allows writers to create an explanation in a place that readers might actually find it.Figure 1. Screenshot of the "Derivative" topic page. View it live at: ourbigbook.com/go/topic/derivativeVideo 2. OurBigBook Web topics demo. Source. - local editing: you can store all your personal knowledge base content locally in a plaintext markup format that can be edited locally and published either:This way you can be sure that even if OurBigBook.com were to go down one day (which we have no plans to do as it is quite cheap to host!), your content will still be perfectly readable as a static site.

- to OurBigBook.com to get awesome multi-user features like topics and likes

- as HTML files to a static website, which you can host yourself for free on many external providers like GitHub Pages, and remain in full control

Figure 2. You can publish local OurBigBook lightweight markup files to either OurBigBook.com or as a static website.Figure 3. Visual Studio Code extension installation.Figure 5. . You can also edit articles on the Web editor without installing anything locally. Video 3. Edit locally and publish demo. Source. This shows editing OurBigBook Markup and publishing it using the Visual Studio Code extension. - Infinitely deep tables of contents:

All our software is open source and hosted at: github.com/ourbigbook/ourbigbook

Further documentation can be found at: docs.ourbigbook.com

Feel free to reach our to us for any help or suggestions: docs.ourbigbook.com/#contact