Free chemistry database Created 2025-01-29 Updated 2025-07-16

List of states of matter Created 2025-01-29 Updated 2025-07-16

Chemistry database Created 2025-01-29 Updated 2025-07-16

Asian American Created 2025-01-28 Updated 2025-07-16

Asian Created 2025-01-28 Updated 2025-07-16

Integration Bee Created 2025-01-28 Updated 2025-07-16

Symbolic integration Created 2025-01-28 Updated 2025-07-16

Computer algebra Created 2025-01-28 Updated 2025-07-16

Fluorine Created 2025-01-28 Updated 2025-07-16

Ion selective electrode Created 2025-01-28 Updated 2025-07-16

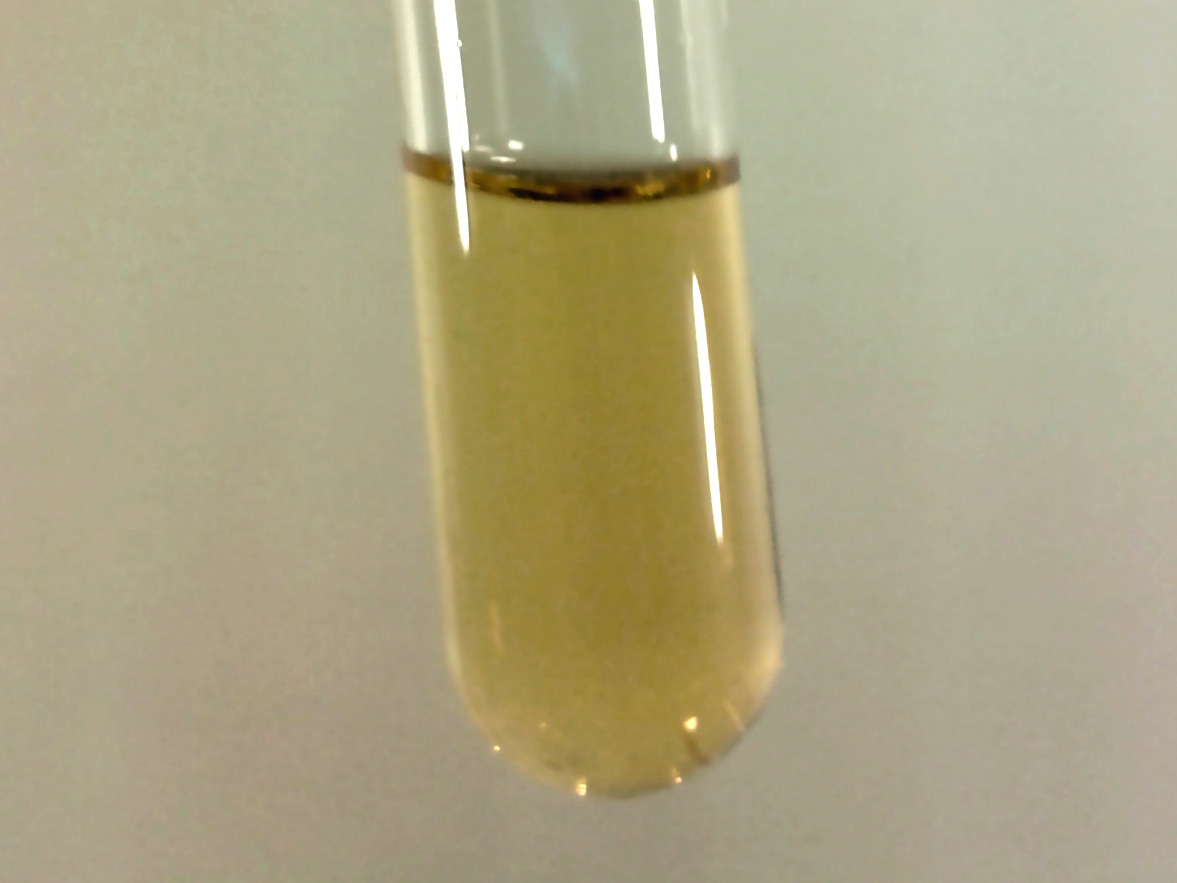

An ion selective electrode is tool used in analytical chemistry used to determine the concentration of a given ion in a solution.

The method can determine the concentration of one ion even if there are multiple different types of ion in the solution, although in some cases this can alter the results. This is done with the help of a selective membrane that only allows certain ions through.

One cool example application mentioned on LibreTexts[ref] is the measurement of fluorine concentration in water. They explain that fluorine is added to the drinking water supply in some countries to help protect people's teeth, and so you want to be able to measure as part of quality control to make sure it is being added in correct the quantities.

The method requires calibrating with calibrating solutions which takes one hour, but once you are calibrated you just stick the sensor into the analyte and get readings in a minute without any expendables. The membrane seems to be a bit fragile which requires care, but overall it looks like a convenient method.

Ion selective electrode schematic

. Source. Sample calibration curve for an ion selective electrode

. Source. The curve is simple and log linear, so once you have that it is easy to fit new measurements to the curve.General Principles of Ion Selective Electrodes by Jacob Stewart

. Source. Ion selective electrodes Tech Tips by Vernier

. Source. It seems like a proprietary training video given with the product that this Peruvian university decided to upload to YouTube. Heroes.

Using an Ion Selective Electrode by University of Alberta

. Source. Analytical chemistry method Created 2025-01-28 Updated 2025-07-16

Analyte Created 2025-01-28 Updated 2025-07-16

Nomacs Created 2025-01-27 Updated 2025-07-16

Image manipulation software Created 2025-01-27 Updated 2025-07-16

Image viewer Created 2025-01-27 Updated 2025-07-16

The Eighth Day of Creation Created 2025-01-27 Updated 2025-07-16

The author Horace Freeland Judson was a MacArthur fellow, no wonder he found the time to write this bible!

On the Internet Archive Open Library:

Max Delbrück is quoted as saying:Nice way to put it.

When Thomas F. Anderson had started taking and publishing the first phage electron microscope images:

Now, Anderson later wrote, "We could really see the phage as tadpole shaped particles, whose heads ranged from 600 to 800 A [...] Anderson wrote. "I remember particularly the reaction of Alfred Hershey's teacher, kindly old Professor J. J. Bronfenbrenner, who had worked on bacteriophages for many years at Washington University in St. Louis. ... When he first saw our pictures ... he clapped the palm of his hand to his forehead and exclaimed, 'Mein Gott! They've got tails!'"

Nice quote from Pauling's Nobel Prize speech highlighting the power and required accuracy of chemical ball and stick models:

The requirements are stringent ones. [...]. In order that the principles of modem structural chemistry may be applied with the power that their reliability justifies, molecular models must be constructed with great accuracy. For example, molecular models on the scale of 2.5 cm 1 angstrom unit, have to be made with a precision better than 0.01 cm.

Image software Created 2025-01-27 Updated 2025-07-16

History of molecular biology bibliography Created 2025-01-27 Updated 2025-07-16

History of molecular biology Created 2025-01-27 Updated 2025-07-16

Bayes' theorem Created 2025-01-27 Updated 2025-07-16

Unlisted articles are being shown, click here to show only listed articles.