"Infinite Worlds" is a science fiction book by the author and filmmaker, John McLoughlin, known for engaging narratives that explore complex themes. However, without specific details about whether you are referring to a particular edition or a specific aspect of the book, I'm unable to provide more precise information. The title may also refer to concepts of multiverses or parallel dimensions, often explored in various science fiction literature.

"Shadows of the Mind" can refer to various works across different media, including literature, films, video games, and more. The title has been utilized in contexts ranging from psychological thrillers to fantasy narratives.

"Light: Science & Applications" is a peer-reviewed scientific journal that focuses on research and developments in the field of photonics and light-based technologies. It covers a wide range of topics, including but not limited to: - Fundamental studies of light and its interactions with matter. - Advances in optical materials and devices. - Applications of light in various fields such as telecommunications, sensing, imaging, and medicine.

The Imaging Science Journal is a publication that focuses on the field of imaging science, which encompasses a range of topics related to the capture, processing, analysis, and interpretation of images. This can include various forms of imaging such as photography, medical imaging, remote sensing, and digital imaging technologies. Typically, the journal publishes peer-reviewed articles, research papers, reviews, and technical notes that contribute to the advancement of knowledge in imaging science.

XLISP is a dialect of the Lisp programming language designed for educational, research, and prototyping purposes. It was developed by David Betz in the late 1980s and is known for its simplicity and small size compared to other Lisp implementations. XLISP supports many of the foundational features of Lisp, including functional programming, object-oriented programming, and integration with C.

As of my last knowledge update in October 2021, Andrew Pinder may refer to different individuals, depending on the context. If you have a specific field or context in mind, please provide more details, and I can offer more targeted information. For example, one notable Andrew Pinder was involved in the field of technology and digital rights, and there may be others in different professions or areas of interest.

Inquiry-based learning is an educational approach that emphasizes the importance of student-driven inquiry and discovery as a means of exploring and understanding complex subjects. Rather than focusing solely on the transmission of facts from teacher to student, inquiry-based learning encourages learners to ask questions, investigate issues, and construct their own understanding through exploration and problem-solving. Key characteristics of inquiry-based learning include: 1. **Question-Driven:** The learning process begins with questions posed by students or teachers, encouraging curiosity and exploration.

The "Cynic epistles" refers to a collection of letters attributed to the ancient Greek philosopher Diogenes of Sinope and other Cynics, although Diogenes himself did not actually write any letters. Rather, these epistles were written by later followers or thinkers influenced by Cynic philosophy. The letters often embody the teachings and principles of Cynicism, emphasizing themes such as self-sufficiency, disdain for societal norms, and a focus on living in accordance with nature.

"De rerum natura," which translates to "On the Nature of Things," is a philosophical poem written by the ancient Roman poet and philosopher Lucretius in the 1st century BCE. It is one of the most significant works of Epicurean philosophy and offers an exploration of nature, the universe, and human existence.

The "Principal Doctrines" often refers to a collection of key philosophical ideas attributed to the ancient Greek philosopher Epicurus, who lived from 341 to 270 BCE. Epicurus was the founder of Epicureanism, a school of thought that emphasized the pursuit of happiness through the cultivation of friendships, the enjoyment of simple pleasures, and the avoidance of pain and fear.

The Olivetti M24 is a personal computer that was released in the early 1980s by the Italian company Olivetti. It was part of Olivetti's efforts to enter the growing market for personal computing during that era. The M24 was notably compatible with IBM PCs, which allowed it to run a variety of software designed for IBM's PC architecture.

South American websites encompass a wide range of platforms and services that cater to users in South America. These can include news sites, e-commerce platforms, social media, government services, and more, often tailored to the specific needs and cultures of the people in various South American countries. Here are some notable examples: 1. **E-commerce**: - **Mercado Livre** (www.mercadolivre.com.br): The largest e-commerce platform in Brazil and widely used across other South American countries.

The English Electric DEUCE is a transistorized computer system developed in the early 1960s in the United Kingdom. It was designed by English Electric's Computing Machine Laboratory and aimed to be an advanced computing system suitable for various scientific and industrial applications. The DEUCE was notable for being one of the first computers to utilize transistor technology instead of vacuum tubes, which resulted in improvements in reliability, speed, and power consumption.

The Ferranti Perseus is a computer system that was produced by the Ferranti company in the late 1950s and early 1960s. It was notable for being one of the early examples of a transistorized computer, designed to be more reliable and efficient than earlier vacuum tube-based machines. The Perseus was primarily used in scientific and engineering applications, where it provided significant advancements in computing capabilities at the time.

The ICT 1900 series, also known as the DCS (Digital Cellular System) 1900, refers to a set of digital mobile telecommunication standards that were developed for use in the 1900 MHz band. This system primarily serves as the foundation for second-generation (2G) mobile networks in North America and is a variant of the Global System for Mobile Communications (GSM) standard used in many other parts of the world.

The term "List of British computers" generally refers to a compilation of notable computers that were designed and manufactured in the United Kingdom. Britain has a rich history of computing, with several significant contributions to the field. Key examples include: 1. **Colossus** (1943) - The first programmable digital computer, used for codebreaking during World War II. 2. **Manchester Mark I** (1949) - One of the earliest stored-program computers.

The Manchester Mark 1 was one of the earliest stored-program computers, developed at the University of Manchester in the United Kingdom in the late 1940s. It was completed in 1949 and was a significant advancement in computing technology for its time. The Manchester Mark 1 was based on earlier designs and was built using vacuum tube technology.

ICL (International Computers Limited) was a British company that produced a range of computer systems, including minicomputers. Founded in the 1960s, ICL was known for its contributions to the development of computing technology in the UK and had a significant presence in the business computing market. Minicomputers are a class of smaller, less powerful computers than mainframes but more powerful than microcomputers.

British internet celebrities encompass a diverse range of individuals who have gained fame and recognition primarily through online platforms such as YouTube, Instagram, TikTok, Twitter, and other social media channels. These personalities can be influencers, content creators, vloggers, and entertainers who create various types of content, including comedy, lifestyle, beauty, gaming, and more.

Pinned article: Introduction to the OurBigBook Project

Welcome to the OurBigBook Project! Our goal is to create the perfect publishing platform for STEM subjects, and get university-level students to write the best free STEM tutorials ever.

Everyone is welcome to create an account and play with the site: ourbigbook.com/go/register. We belive that students themselves can write amazing tutorials, but teachers are welcome too. You can write about anything you want, it doesn't have to be STEM or even educational. Silly test content is very welcome and you won't be penalized in any way. Just keep it legal!

Intro to OurBigBook

. Source. We have two killer features:

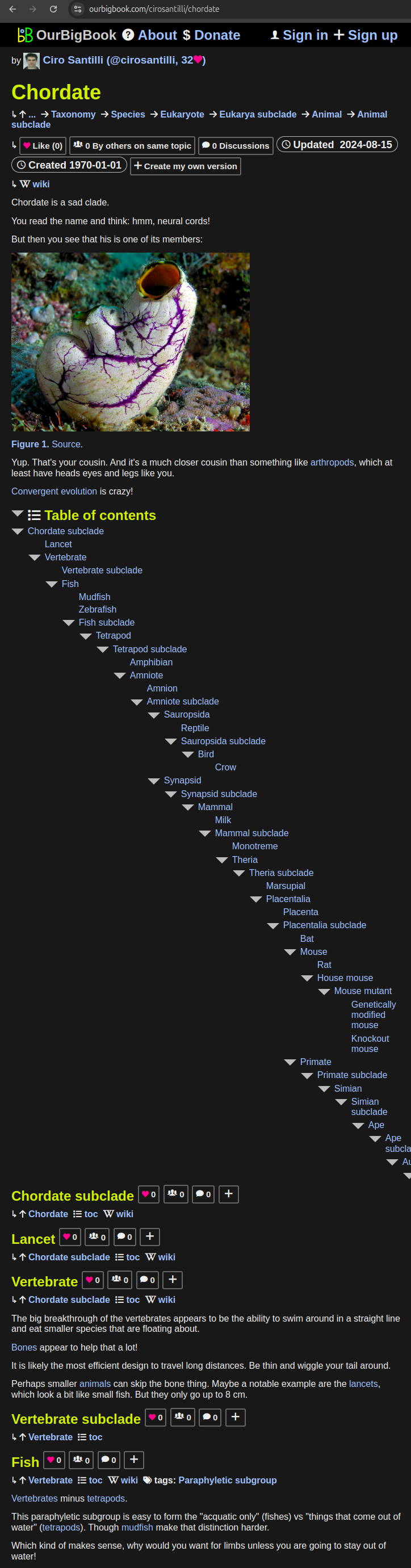

- topics: topics group articles by different users with the same title, e.g. here is the topic for the "Fundamental Theorem of Calculus" ourbigbook.com/go/topic/fundamental-theorem-of-calculusArticles of different users are sorted by upvote within each article page. This feature is a bit like:

- a Wikipedia where each user can have their own version of each article

- a Q&A website like Stack Overflow, where multiple people can give their views on a given topic, and the best ones are sorted by upvote. Except you don't need to wait for someone to ask first, and any topic goes, no matter how narrow or broad

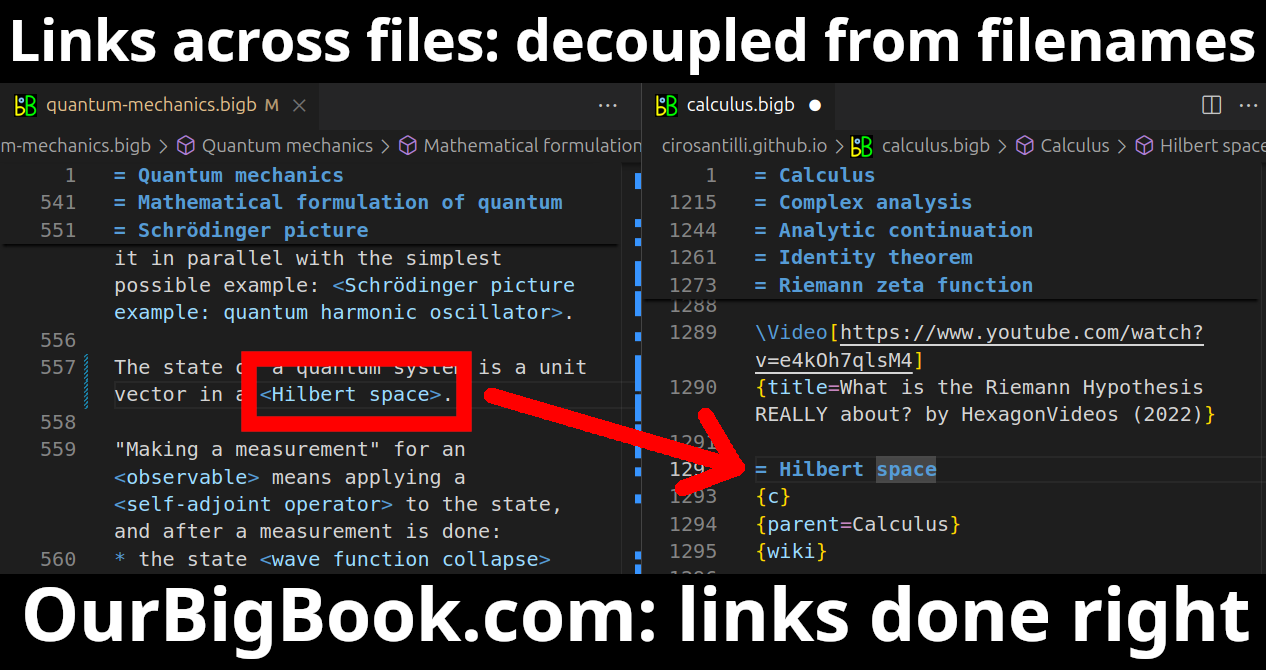

This feature makes it possible for readers to find better explanations of any topic created by other writers. And it allows writers to create an explanation in a place that readers might actually find it.Figure 1. Screenshot of the "Derivative" topic page. View it live at: ourbigbook.com/go/topic/derivativeVideo 2. OurBigBook Web topics demo. Source. - local editing: you can store all your personal knowledge base content locally in a plaintext markup format that can be edited locally and published either:This way you can be sure that even if OurBigBook.com were to go down one day (which we have no plans to do as it is quite cheap to host!), your content will still be perfectly readable as a static site.

- to OurBigBook.com to get awesome multi-user features like topics and likes

- as HTML files to a static website, which you can host yourself for free on many external providers like GitHub Pages, and remain in full control

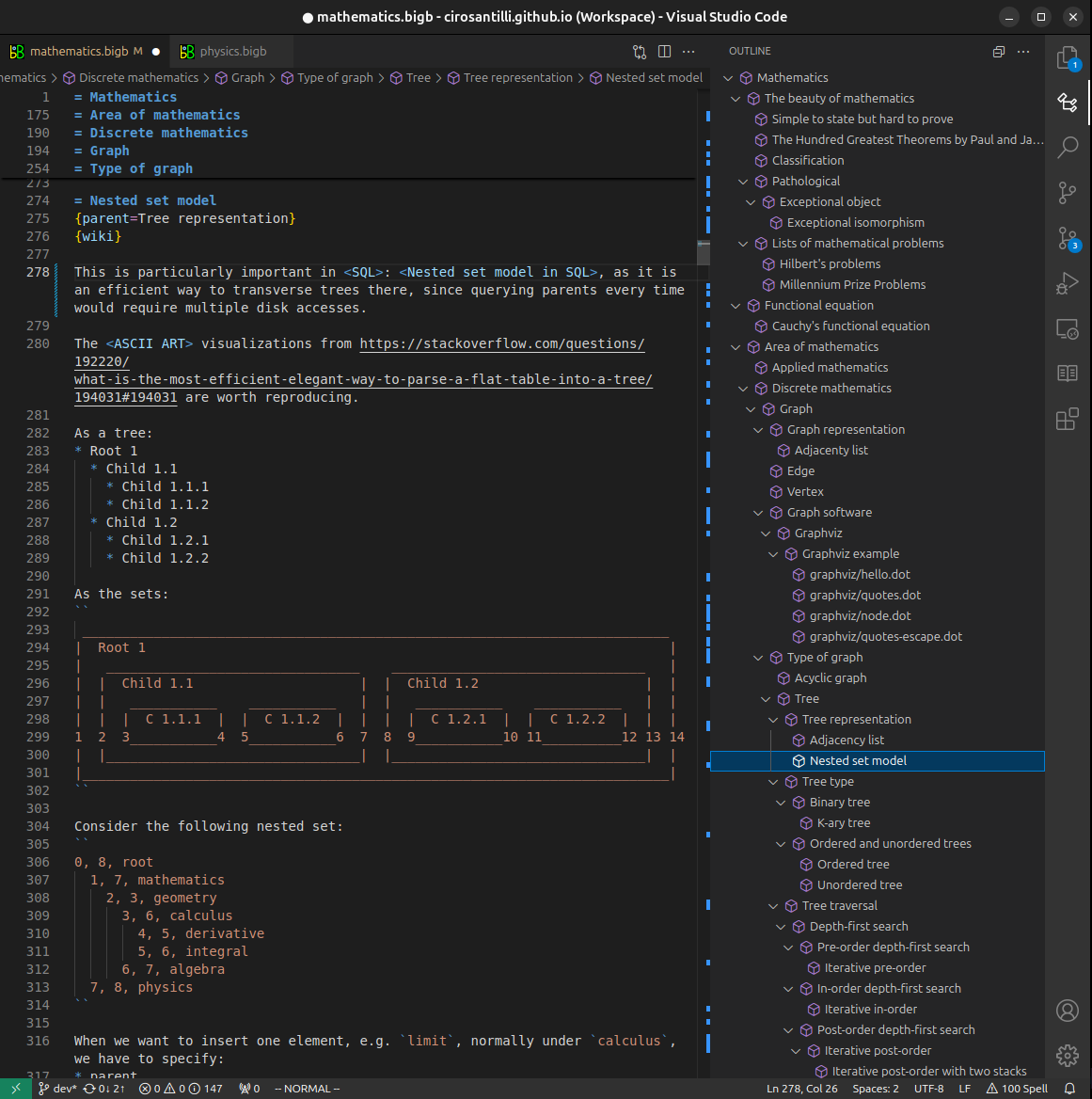

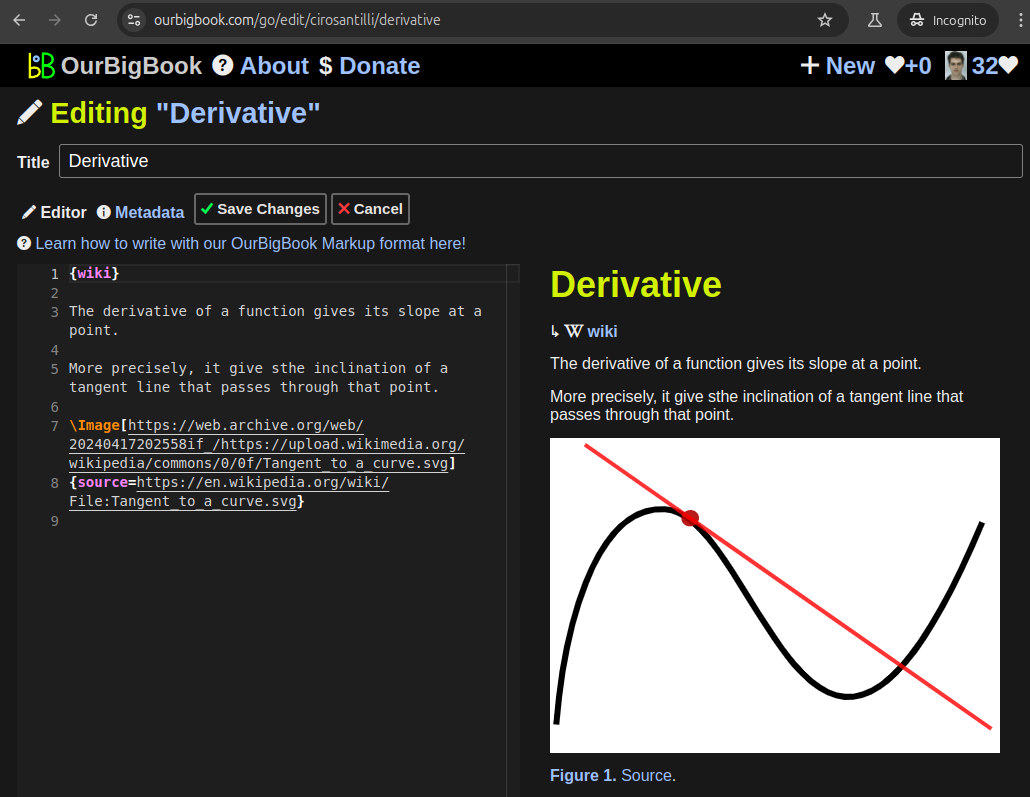

Figure 3. Visual Studio Code extension installation.Figure 4. Visual Studio Code extension tree navigation.Figure 5. Web editor. You can also edit articles on the Web editor without installing anything locally.Video 3. Edit locally and publish demo. Source. This shows editing OurBigBook Markup and publishing it using the Visual Studio Code extension.Video 4. OurBigBook Visual Studio Code extension editing and navigation demo. Source. - Infinitely deep tables of contents:

All our software is open source and hosted at: github.com/ourbigbook/ourbigbook

Further documentation can be found at: docs.ourbigbook.com

Feel free to reach our to us for any help or suggestions: docs.ourbigbook.com/#contact