The National Academy of Marine Research (NAMR) does not appear to be a widely recognized institution as of my last knowledge update in October 2023. It is possible that you may be referring to a specific organization focused on marine research, but the name might not be widely known or it might be newly established. Marine research is typically conducted by various institutions, including universities, government agencies, and research organizations, that study marine ecosystems, oceanography, marine biology, and related fields.

The National Videotex Network (NVN) refers to an initiative established in the United States in the early 1980s to promote the development and use of videotex services, which were early forms of online information retrieval and communication systems. Videotex systems were designed to provide users with access to text and graphical information via telephone lines, often through dedicated terminals or television sets.

Negation as failure is a concept primarily used in logic programming and non-monotonic reasoning, notably in the field of artificial intelligence and computational logic. It is a way of handling negation in a way that is consistent with the principle of closed world assumption (CWA). In classical logic, a statement can either be true or false, and the truth of a statement can be proven with evidence. However, in many practical applications, we often deal with incomplete knowledge about a system or domain.

Newton–Wigner localization is a concept in quantum mechanics that deals with the localization of quantum particles, especially in the context of relativistic quantum field theories. It was introduced by the physicists T.D. Newton and E.P. Wigner in the 1940s as a way to define the position of relativistic particles. In non-relativistic quantum mechanics, the position of a particle can be represented by the position operator in a straightforward manner.

Nikolai Kapustin is a Russian mathematician known for his work in the fields of functional analysis, operator theory, and noncommutative geometry. He has made significant contributions to the understanding of certain areas of mathematics, particularly involving operator algebras and their applications to mathematical physics. In addition to his research, Kapustin has been involved in various academic roles, including teaching and mentoring students in mathematics.

Nikolay Krasovsky may refer to multiple individuals, but one notable figure by that name is a Russian mathematician, particularly known for his work in the field of mathematical logic and related areas. It’s possible that there may be others with that name in different fields or contexts.

The Normalized Difference Water Index (NDWI) is a remote sensing index used primarily to assess the presence and distribution of water bodies. It helps distinguish between water and non-water features in satellite imagery. The NDWI exploits the reflective properties of water in different parts of the electromagnetic spectrum, particularly focusing on the visible (green) and near-infrared (NIR) wavelengths.

The Northern European Enclosure Dam is a proposed infrastructure project designed to protect Northern European countries from the effects of climate change, particularly rising sea levels and flooding associated with storm surges. The project envisions the construction of a barrier system that would enclose several countries or regions, such as the Netherlands, Germany, Denmark, and potentially others, to mitigate flooding risks and protect coastal areas.

An Online Service Provider (OSP) is a business or organization that offers services to users over the Internet. These services can range widely, covering various categories such as communication, information access, entertainment, and cloud computing. OSPs typically provide platforms and infrastructure that enable users to perform specific tasks or access resources online. Some common types of online service providers include: 1. **Internet Service Providers (ISPs)**: Companies that provide users with access to the Internet.

Orest Khvolson was a Ukrainian-born American mathematician known for his work in functional analysis and the theory of linear operators. He was active in the mid-20th century and contributed to the development of various mathematical theories and concepts. His contributions often intersected with areas such as spectral theory and operator algebras. In addition to his mathematical work, Khvolson is noted for his involvement in education, mentoring students, and promoting mathematical research.

P-adic Hodge theory is a branch of mathematics that lies at the intersection of algebraic geometry, number theory, and representation theory. It provides a framework for understanding the behavior of p-adic forms and their connections to classical geometry.

PASS Sample Size Software is a statistical tool designed to help researchers and analysts determine the appropriate sample size for their studies, ensuring that their analyses have sufficient power to detect effects or differences. The software can handle various types of statistical tests and is often used in fields like clinical research, social sciences, and market research.

The term "interactome" refers to the comprehensive network of molecular interactions within a cell. It encompasses all the interactions that occur between various biomolecules, including proteins, nucleic acids, lipids, and small molecules. The interactome is a key component of systems biology and is essential for understanding the complex biochemical processes that underpin cellular function.

Magnetic-activated cell sorting (MACS) is a technique used to separate and purify specific populations of cells from a mixed cell sample based on their surface antigens. This method utilizes magnetic fields and magnetic microbeads that are linked to antibodies targeting specific cell markers. ### Process Overview: 1. **Antibody Coating**: Cells in a suspension are incubated with magnetic microbeads that are coated with antibodies specific to the surface markers of the target cell population.

The Mal regulon is a set of genes in bacteria, primarily studied in Escherichia coli, that are involved in the transport and metabolism of maltose and maltodextrins. This regulon is typically composed of genes that encode proteins required for the uptake of these sugars and their subsequent breakdown. The main components of the Mal regulon include: 1. **MalT**: The regulatory protein that activates the transcription of the mal genes in response to the presence of maltose.

J-Anomaly Ridge is an underwater geological feature located in the central Atlantic Ocean. It is characterized by a significant positive geoid anomaly that is thought to result from a combination of geological factors, including variations in crustal thickness, mantle dynamics, and volcanic activity. The ridge is part of a broader system of underwater features that reflect the geological processes that shape the ocean floor, including seafloor spreading, tectonic activity, and sedimentation.

János Pach is a prominent Hungarian mathematician known for his contributions to combinatorial geometry, discrete geometry, and related areas. Born on April 21, 1946, he has worked extensively in fields such as convex geometry, incidence geometry, and graph theory. Pach has authored numerous research papers and co-authored books, making significant impacts through both theoretical work and practical applications in mathematics.

Japanese women mathematicians have made significant contributions to various fields of mathematics. Although historically, the representation of women in mathematics, like in many scientific fields, has been limited, there are notable figures who have excelled and paved the way for future generations. Some prominent Japanese women mathematicians include: 1. **Kunihiko Kodaira** - While not a woman, it's important to mention that Kodaira's work has influenced Japanese women mathematicians.

Java Modeling Language (JML) is formal specification language used to describe the behavior of Java modules (classes and interfaces) in a way that is understandable to both humans and computers. JML is an extension of the Java programming language, designed to specify what a program is supposed to do rather than how it does it.

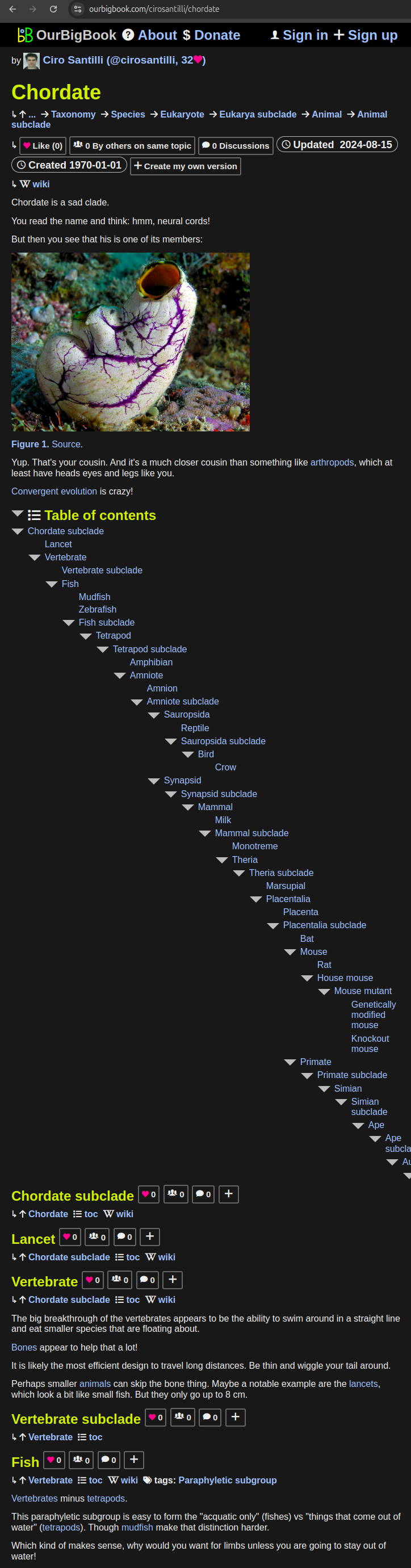

Pinned article: Introduction to the OurBigBook Project

Welcome to the OurBigBook Project! Our goal is to create the perfect publishing platform for STEM subjects, and get university-level students to write the best free STEM tutorials ever.

Everyone is welcome to create an account and play with the site: ourbigbook.com/go/register. We belive that students themselves can write amazing tutorials, but teachers are welcome too. You can write about anything you want, it doesn't have to be STEM or even educational. Silly test content is very welcome and you won't be penalized in any way. Just keep it legal!

Intro to OurBigBook

. Source. We have two killer features:

- topics: topics group articles by different users with the same title, e.g. here is the topic for the "Fundamental Theorem of Calculus" ourbigbook.com/go/topic/fundamental-theorem-of-calculusArticles of different users are sorted by upvote within each article page. This feature is a bit like:

- a Wikipedia where each user can have their own version of each article

- a Q&A website like Stack Overflow, where multiple people can give their views on a given topic, and the best ones are sorted by upvote. Except you don't need to wait for someone to ask first, and any topic goes, no matter how narrow or broad

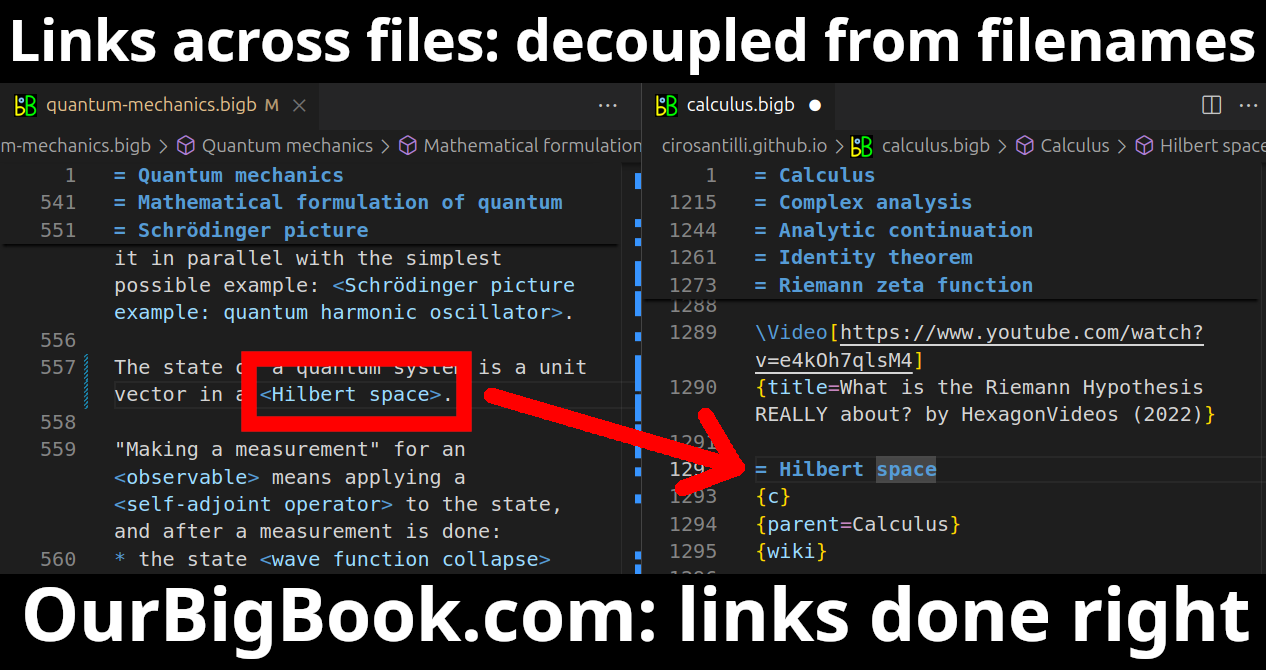

This feature makes it possible for readers to find better explanations of any topic created by other writers. And it allows writers to create an explanation in a place that readers might actually find it.Figure 1. Screenshot of the "Derivative" topic page. View it live at: ourbigbook.com/go/topic/derivativeVideo 2. OurBigBook Web topics demo. Source. - local editing: you can store all your personal knowledge base content locally in a plaintext markup format that can be edited locally and published either:This way you can be sure that even if OurBigBook.com were to go down one day (which we have no plans to do as it is quite cheap to host!), your content will still be perfectly readable as a static site.

- to OurBigBook.com to get awesome multi-user features like topics and likes

- as HTML files to a static website, which you can host yourself for free on many external providers like GitHub Pages, and remain in full control

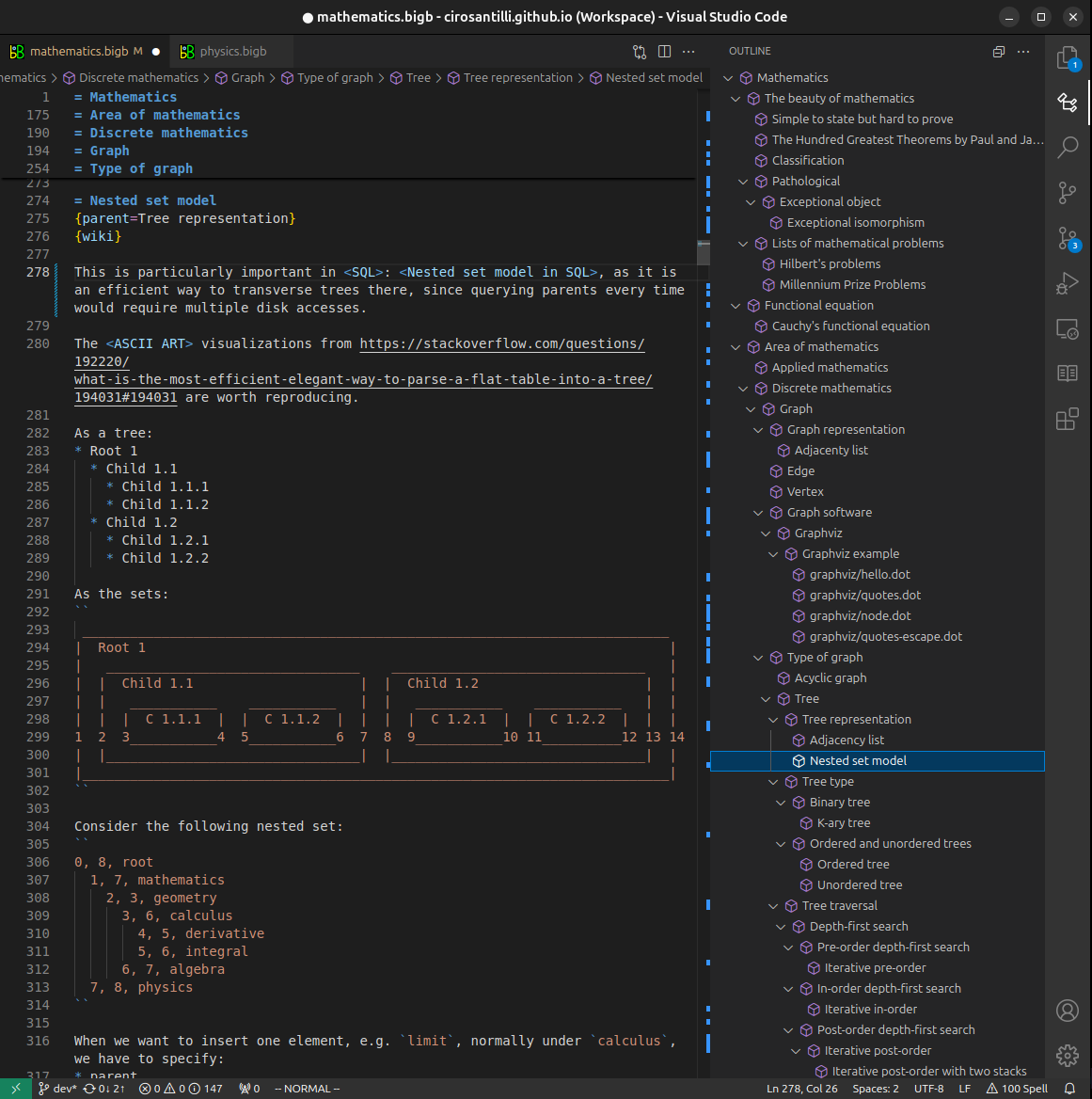

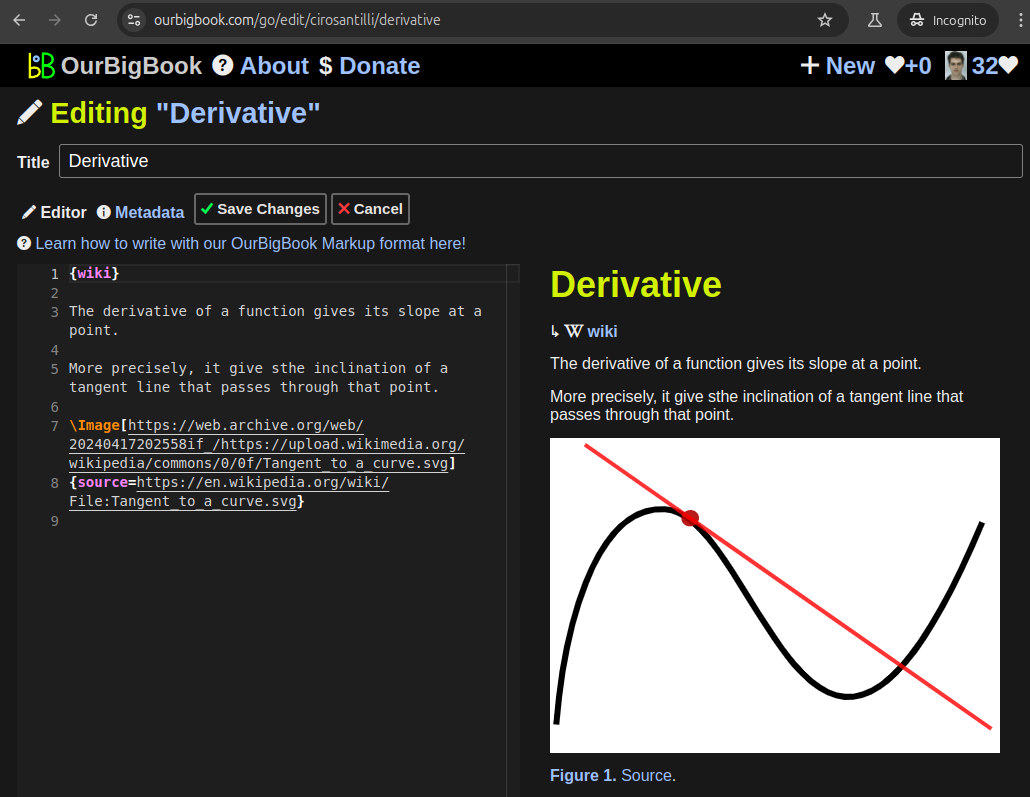

Figure 3. Visual Studio Code extension installation.Figure 4. Visual Studio Code extension tree navigation.Figure 5. Web editor. You can also edit articles on the Web editor without installing anything locally.Video 3. Edit locally and publish demo. Source. This shows editing OurBigBook Markup and publishing it using the Visual Studio Code extension.Video 4. OurBigBook Visual Studio Code extension editing and navigation demo. Source. - Infinitely deep tables of contents:

All our software is open source and hosted at: github.com/ourbigbook/ourbigbook

Further documentation can be found at: docs.ourbigbook.com

Feel free to reach our to us for any help or suggestions: docs.ourbigbook.com/#contact