Space exploration is the investigation and study of outer space through the use of space technology, such as spacecraft, satellites, telescopes, and rovers. It encompasses a variety of activities aimed at understanding celestial bodies, the universe, and the phenomena within it.

The Bogotá Declaration refers to a formal agreement made in Bogotá, Colombia, on September 6, 2021, during the International Conference on Sustainable Development and Health. This declaration emphasized the importance of sustainable urban development and public health, particularly in the context of the COVID-19 pandemic and its long-term impacts on cities and communities.

The interplanetary magnetic field (IMF) is a magnetic field that permeates the space between planets in our solar system. It is primarily carried by the solar wind, which is a stream of charged particles (mainly electrons and protons) emitted by the Sun. The IMF is a manifestation of the solar magnetic field as it extends outward from the Sun into interplanetary space.

A variable buoyancy pressure vessel is a type of underwater vehicle or system specifically designed to control its buoyancy and, consequently, its depth in a fluid, typically water. The key feature of such a vessel is its ability to adjust its buoyancy dynamically, allowing it to ascend or descend in the water column without the need for propulsion.

Windpumps, also known as wind-driven pumps or windmill pumps, are devices that use wind energy to pump water. They have been used for centuries, particularly in agricultural and rural settings, to access groundwater and provide irrigation or drinking water. ### Key Features of Windpumps: 1. **Mechanism**: The basic design typically includes a rotor (or windmill) that captures wind energy, which is then converted into mechanical energy to drive a pumping mechanism.

Archimedes' screw is an ancient device used for raising water, attributed to the Greek mathematician and inventor Archimedes of Syracuse. It consists of a helical screw enclosed in a cylindrical casing. When the screw is turned, typically by turning a crank or other mechanical means, water is lifted from a lower level to a higher level. The design features a spiral thread wrapped around a central rod or axle.

A boiler feedwater pump is a type of pump used to supply water to a steam boiler. The main purpose of the feedwater pump is to deliver water to the boiler at high pressure, ensuring that the boiler can generate steam efficiently and effectively for various applications, such as power generation, heating, and industrial processes.

An electromagnetic pump is a type of pump that uses electromagnetic forces to move conductive liquids or slurries. These pumps operate on the principle of electromagnetic induction and are commonly used in applications involving molten metals, electrolytes, and other conductive fluids. ### Working Principle: The basic operation of an electromagnetic pump involves the following key components: 1. **Conductive Fluid**: The fluid being pumped must be electrically conductive, such as molten metals (e.g., aluminum, zinc) or electrochemical solutions.

A fire pump is a part of a fire protection system that is designed to move water or other fire suppression agents through a system of pipes to extinguish or control a fire. Fire pumps are critical in providing the necessary water pressure and flow rate for firefighting efforts, especially in locations where the municipal water supply is insufficient or unavailable.

"Honda pumps" typically refer to a range of water pumps manufactured by Honda, a well-known Japanese company recognized for its engines and machinery. Honda produces various types of pumps, including: 1. **Portable Water Pumps**: These are designed for general water transfer applications, such as draining pools, moving water for irrigation, or general cleanup tasks.

The Quasiturbine is a type of rotary engine that was developed as an alternative to traditional internal combustion engines. It was invented by French engineer Michel Pêne in the 1990s. The Quasiturbine operates based on a novel design that aims to provide high efficiency, reduced emissions, and improved power output compared to conventional piston engines.

A submersible pump is a type of pump designed to be submerged in a liquid, typically water. It consists of a motor and a pump body that are enclosed in a single housing. Submersible pumps are used to move fluids from lower to higher elevations, and they operate by pushing the fluid to the surface rather than pulling it, which is advantageous for lifting liquids over long distances or to considerable heights.

Szczecin pumps refer to a specific type of pumping equipment or system, but it could also refer to a brand or a product associated with the city of Szczecin, Poland. Szczecin is known for various industries, including shipbuilding and maritime activities, which may involve pumps used in shipping, water management, or other industrial applications.

Ecological robots, often referred to as "eco-robots," are autonomous or semi-autonomous robotic systems designed to monitor, manage, and restore ecological environments. Their primary purpose is to assist in tasks related to environmental conservation, agriculture, and sustainability. Here are some key aspects of ecological robots: 1. **Environmental Monitoring**: Eco-robots can collect data on various environmental parameters, such as air and water quality, soil conditions, and biodiversity.

The regulation of robots refers to the legal, ethical, and operational frameworks that govern the design, development, deployment, and use of robotic systems. As robotics technology advances and becomes more integrated into various sectors like healthcare, manufacturing, transportation, and even domestic environments, regulatory oversight is increasingly important to ensure safety, liability, ethical considerations, and societal impacts.

"Robots by country" typically refers to the number and distribution of robots deployed in various countries, which can include industrial robots, service robots, and other types of automated machinery. The statistics on robots can vary based on factors like industrialization, economic development, and technology adoption in various regions.

Sports robots are robotic systems designed to participate in, assist with, or enhance various aspects of sports and athletic activities. These robots can take on a wide range of forms and functions, which may include: 1. **Robotic Athletes**: Some robots are designed to compete in sports, showcasing advanced engineering and programming. Examples include robot soccer players, race cars, or even humanoid robots designed for specific sports.

Uncrewed vehicles, also known as unmanned vehicles, are vehicles that operate without a human presence on board. These vehicles can be remotely controlled or operate autonomously through pre-programmed instructions or artificial intelligence. Uncrewed vehicles can be categorized into several types, including: 1. **Uncrewed Aerial Vehicles (UAVs)**: Commonly known as drones, these vehicles are used for various applications, including aerial photography, surveillance, agricultural monitoring, and delivery services.

A "bang-bang robot" typically refers to a type of control system used in robotics, particularly in the context of actuators and motion control. The term "bang-bang" describes a control strategy that toggles between two extreme states, akin to an on-off control mechanism. This type of control system is characterized by: 1. **Binary Control**: The actuator is either fully engaged or completely disengaged, with no intermediate positions.

Cable robots, also known as cable-driven robots or cable-suspended robots, are robotic systems that utilize cables or wires for movement and support. They are typically characterized by a lightweight design and the ability to move in three-dimensional space by controlling the lengths of multiple cables connected to a central platform or end effector. The movement is typically realized through the actuation of motors or winches that adjust the tension on the cables.

Pinned article: Introduction to the OurBigBook Project

Welcome to the OurBigBook Project! Our goal is to create the perfect publishing platform for STEM subjects, and get university-level students to write the best free STEM tutorials ever.

Everyone is welcome to create an account and play with the site: ourbigbook.com/go/register. We belive that students themselves can write amazing tutorials, but teachers are welcome too. You can write about anything you want, it doesn't have to be STEM or even educational. Silly test content is very welcome and you won't be penalized in any way. Just keep it legal!

Intro to OurBigBook

. Source. We have two killer features:

- topics: topics group articles by different users with the same title, e.g. here is the topic for the "Fundamental Theorem of Calculus" ourbigbook.com/go/topic/fundamental-theorem-of-calculusArticles of different users are sorted by upvote within each article page. This feature is a bit like:

- a Wikipedia where each user can have their own version of each article

- a Q&A website like Stack Overflow, where multiple people can give their views on a given topic, and the best ones are sorted by upvote. Except you don't need to wait for someone to ask first, and any topic goes, no matter how narrow or broad

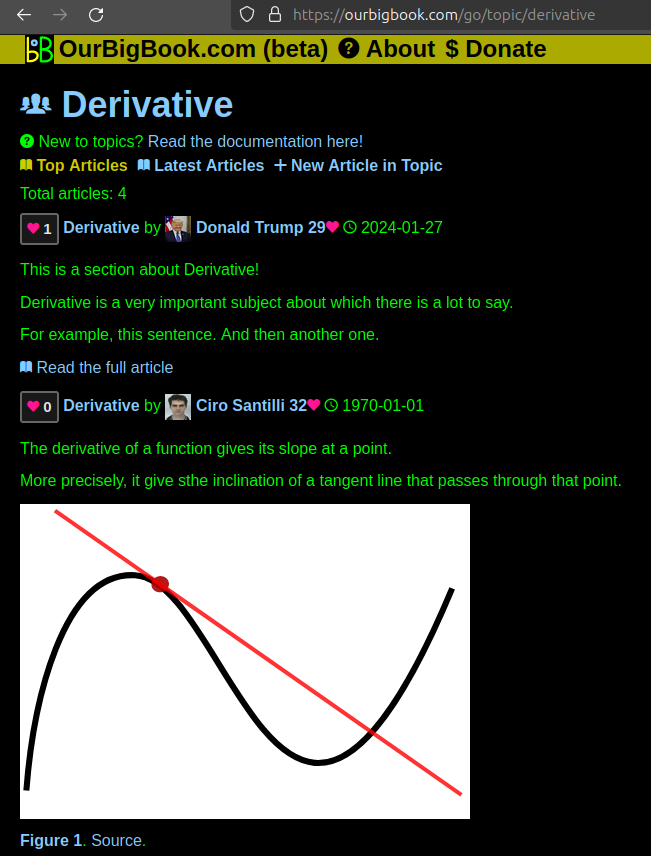

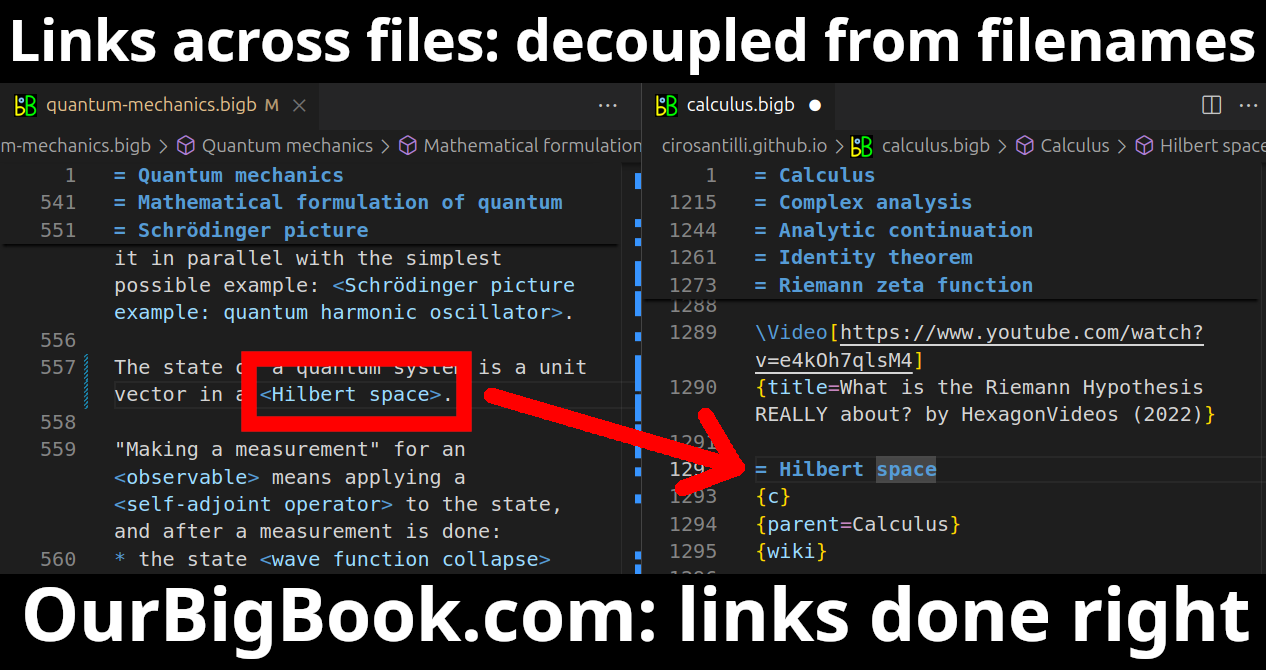

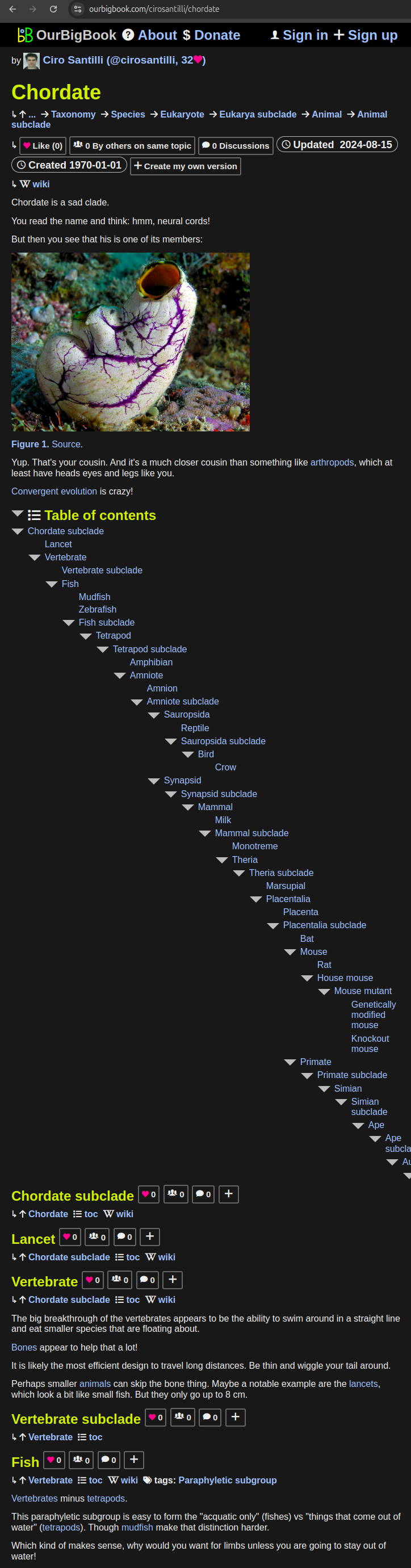

This feature makes it possible for readers to find better explanations of any topic created by other writers. And it allows writers to create an explanation in a place that readers might actually find it.Figure 1. Screenshot of the "Derivative" topic page. View it live at: ourbigbook.com/go/topic/derivativeVideo 2. OurBigBook Web topics demo. Source. - local editing: you can store all your personal knowledge base content locally in a plaintext markup format that can be edited locally and published either:This way you can be sure that even if OurBigBook.com were to go down one day (which we have no plans to do as it is quite cheap to host!), your content will still be perfectly readable as a static site.

- to OurBigBook.com to get awesome multi-user features like topics and likes

- as HTML files to a static website, which you can host yourself for free on many external providers like GitHub Pages, and remain in full control

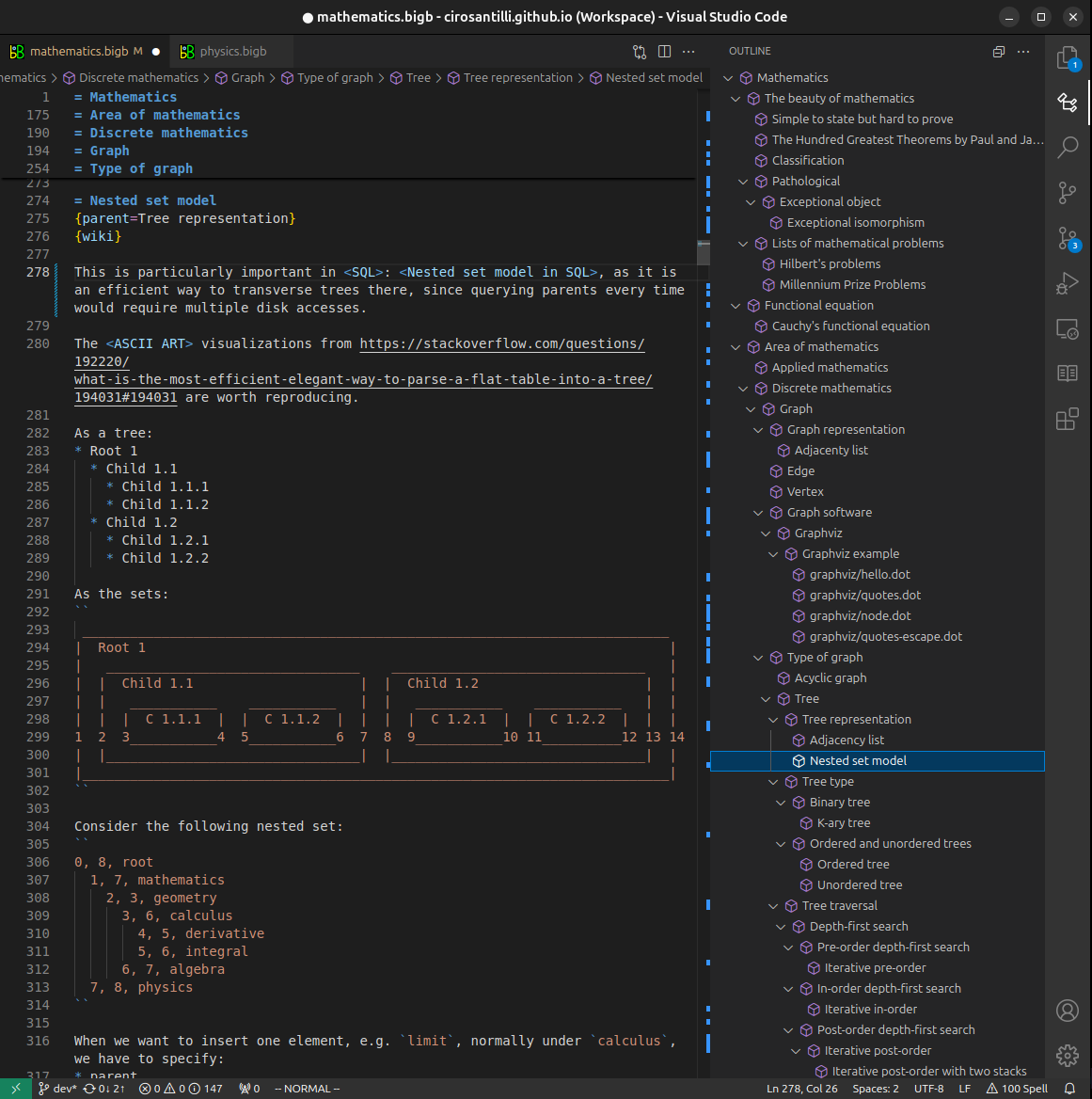

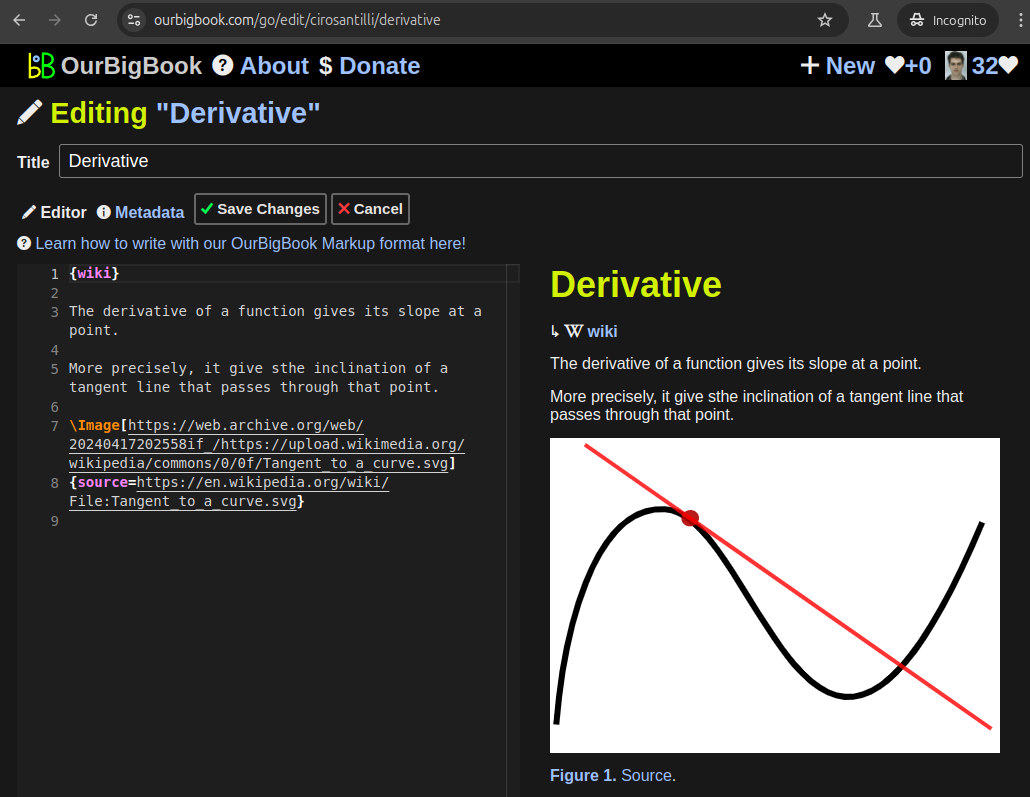

Figure 3. Visual Studio Code extension installation.Figure 4. Visual Studio Code extension tree navigation.Figure 5. Web editor. You can also edit articles on the Web editor without installing anything locally.Video 3. Edit locally and publish demo. Source. This shows editing OurBigBook Markup and publishing it using the Visual Studio Code extension.Video 4. OurBigBook Visual Studio Code extension editing and navigation demo. Source. - Infinitely deep tables of contents:

All our software is open source and hosted at: github.com/ourbigbook/ourbigbook

Further documentation can be found at: docs.ourbigbook.com

Feel free to reach our to us for any help or suggestions: docs.ourbigbook.com/#contact