The Erdős–Faber–Lovász conjecture is a famous open problem in graph theory, specifically in the field of combinatorial mathematics. It was proposed by mathematicians Paul Erdős, V. T. Faber, and László Lovász in 1972. The conjecture concerns the coloring of graphs formed by a specific construction.

Eric Hehner is a notable figure in the field of computer science, particularly known for his work in programming language theory and formal methods. He has made significant contributions to the development of techniques for specifying and reasoning about computer programs. Hehner is often associated with concepts such as formal specification, program correctness, and the use of logical frameworks in software development. His work includes the design and implementation of programming languages, as well as research on the principles and fundamentals of computing.

Ernst Hölder was a German mathematician known for his contributions to various fields of mathematics, particularly in analysis and number theory. He is best known for Hölder's inequality, which is a fundamental result in functional analysis and a key tool in various areas of mathematics, including probability theory and statistics.

Etching is a printmaking technique that involves using acid to carve designs into the surface of a metal plate, typically made of copper, zinc, or steel. The process generally involves the following steps: 1. **Preparation of the Plate**: The metal plate is cleaned and coated with a layer of wax or a similar material called a ground. This ground will resist acid.

The European Association of Geoscientists and Engineers (EAGE) is a professional organization that focuses on the advancement of geosciences and engineering, primarily in the fields of earth sciences, geophysics, geology, petroleum engineering, and environmental engineering. Founded in 1951, EAGE serves as a platform for professionals in these disciplines to share knowledge, network, and collaborate on research and development.

Event monitoring refers to the systematic observation and analysis of events, activities, or occurrences to gather data and insights that can inform decision-making, enhance security, or improve operations. This concept is widely applied in various fields, including information technology, event management, security, marketing, and healthcare.

Evolutionary linguistics is a field of study that examines the origins and development of language through the lens of evolutionary theory. It seeks to understand how language may have evolved in humans, both as a cognitive ability and as a means of communication, as part of the broader evolutionary changes in hominins. This interdisciplinary approach combines insights from linguistics, anthropology, cognitive science, biology, and evolutionary psychology.

The evolution from the Francis turbine to the Kaplan turbine represents significant advancements in hydraulic turbine technology, reflecting changes in design, efficiency, and operating conditions for hydroelectric power generation. ### Francis Turbine 1. **Introduction**: The Francis turbine, developed by James B. Francis in the mid-19th century, was one of the first efficient types of turbines for medium to high head applications. It operates on the principle of converting hydraulic energy into mechanical energy.

Ezra Getzler is an academic known for his work in mathematics, particularly in the field of dynamical systems and mathematical biology. He is associated with creating mathematical models that explore complex systems and their behaviors.

In functional analysis, the concept of extensions of symmetric operators plays a crucial role, particularly in the context of unbounded operators on Hilbert spaces. Here’s an overview of the key aspects of this topic: ### Symmetric Operators 1.

External debt refers to the portion of a country's total debt that is owed to foreign creditors. This can include loans from foreign governments, international financial institutions (like the International Monetary Fund or World Bank), private banks, or individual investors located outside the debtor country. External debt can be denominated in foreign currencies and generally includes both principal and interest payments. External debt can be an important aspect of a country's economy, as it can provide much-needed capital for development, infrastructure, and other projects.

External sorting is a technique used for sorting large amounts of data that cannot fit into the computer's main memory (RAM) at once. This is common in cases where datasets are larger than the available RAM, such as sorting files stored on disk, databases, or processing large data streams. ### Key Features and Concepts of External Sorting: 1. **External Storage**: External sorting typically involves data that resides on external storage devices, such as hard drives or SSDs, rather than being held in RAM.

The Falkland Current is a cold ocean current that flows northward along the eastern coast of South America, primarily along the continental shelf off the coast of Argentina. It originates from the Antarctic Circumpolar Current and is influenced by the cold waters of the South Atlantic Ocean. The Falkland Current plays a significant role in the regional marine ecosystem and climate. It contributes to the upwelling of nutrients, which supports rich marine biodiversity, including important fisheries.

"Fallout" is a television series based on the popular video game franchise of the same name, developed by Bethesda Game Studios and published by Bethesda Softworks. The series was announced in 2020 and is produced by Amazon Prime Video. The show aims to capture the post-apocalyptic themes and unique storytelling elements that have characterized the Fallout games, which are set in a retro-futuristic world affected by nuclear war.

A homology sphere is a topological space that behaves like a sphere in terms of its homological properties, even if it is not actually a sphere in the classical sense. More formally, an \( n \)-dimensional homology sphere is a manifold that is homotopy equivalent to the \( n \)-dimensional sphere \( S^n \), and, importantly, it has the same homology groups as \( S^n \).

Glycomimetics are synthetic compounds designed to mimic the structures and functions of carbohydrates (glycans) in biological systems. These molecules can interact with proteins that recognize sugars, such as lectins or glycan-binding proteins, and are often employed to modulate biological processes.

Faster-than-light (FTL) travel refers to the hypothetical concept of traveling faster than the speed of light, which is approximately 299,792 kilometers per second (186,282 miles per second) in a vacuum. According to our current understanding of physics, particularly Einstein's theory of relativity, as an object approaches the speed of light, its mass increases, and it would require an infinite amount of energy to actually reach or exceed that speed.

Father Time is often depicted as a personification of time, typically represented as an old man with a long beard, carrying a scythe and an hourglass. This figure embodies the passage of time and the inevitability of aging and death. In various cultural depictions, Father Time is contrasted with the concept of the New Year or youth, symbolizing the cyclical nature of life.

Pinned article: Introduction to the OurBigBook Project

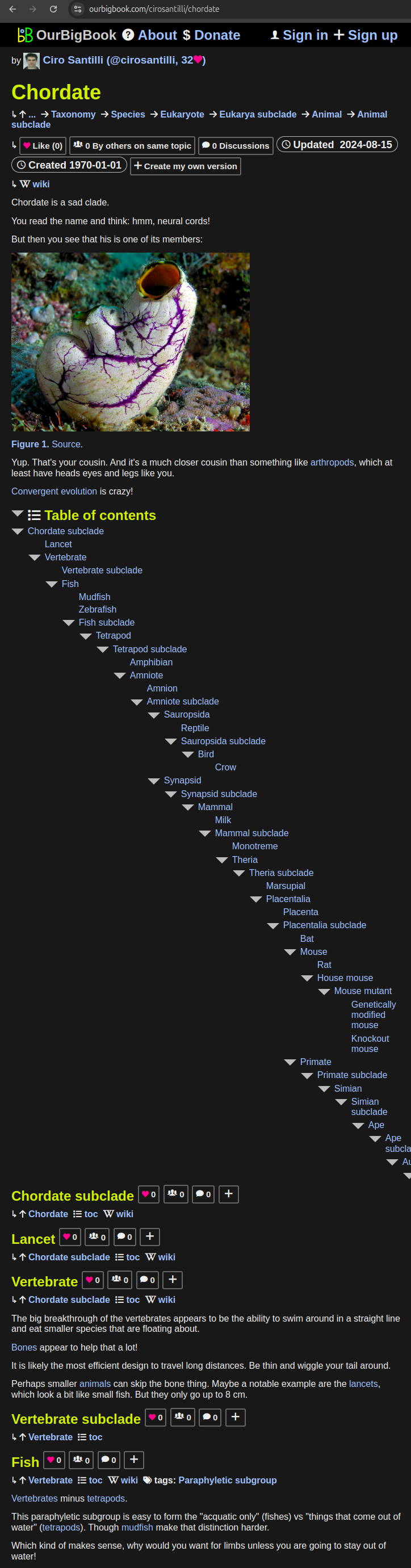

Welcome to the OurBigBook Project! Our goal is to create the perfect publishing platform for STEM subjects, and get university-level students to write the best free STEM tutorials ever.

Everyone is welcome to create an account and play with the site: ourbigbook.com/go/register. We belive that students themselves can write amazing tutorials, but teachers are welcome too. You can write about anything you want, it doesn't have to be STEM or even educational. Silly test content is very welcome and you won't be penalized in any way. Just keep it legal!

Intro to OurBigBook

. Source. We have two killer features:

- topics: topics group articles by different users with the same title, e.g. here is the topic for the "Fundamental Theorem of Calculus" ourbigbook.com/go/topic/fundamental-theorem-of-calculusArticles of different users are sorted by upvote within each article page. This feature is a bit like:

- a Wikipedia where each user can have their own version of each article

- a Q&A website like Stack Overflow, where multiple people can give their views on a given topic, and the best ones are sorted by upvote. Except you don't need to wait for someone to ask first, and any topic goes, no matter how narrow or broad

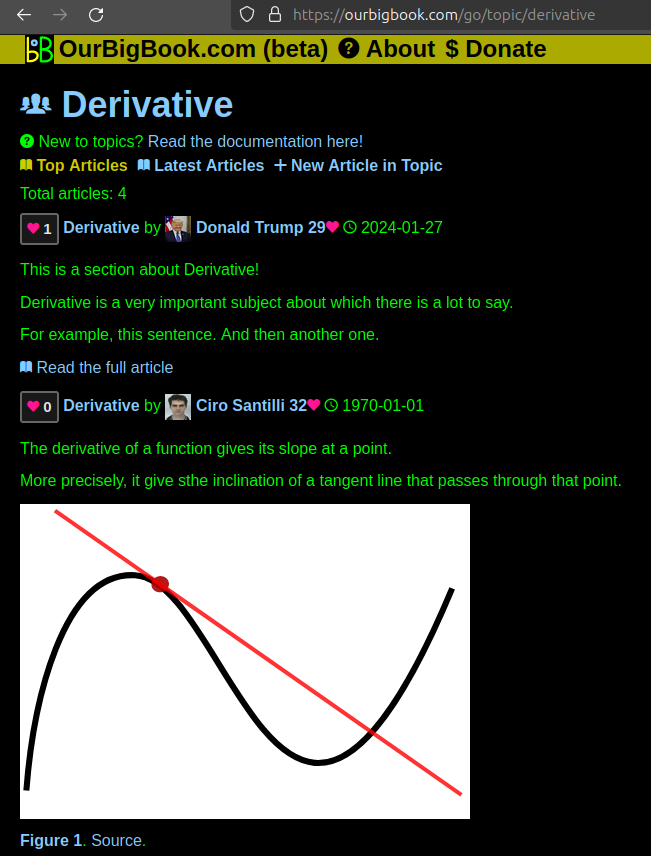

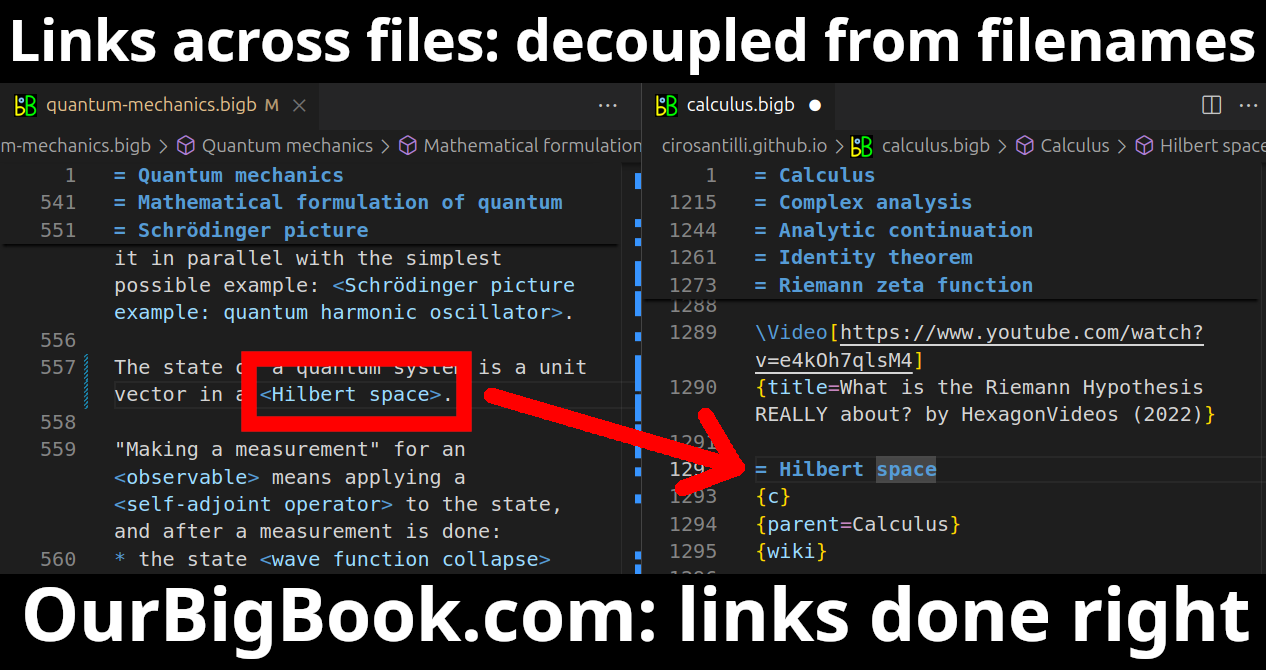

This feature makes it possible for readers to find better explanations of any topic created by other writers. And it allows writers to create an explanation in a place that readers might actually find it.Figure 1. Screenshot of the "Derivative" topic page. View it live at: ourbigbook.com/go/topic/derivativeVideo 2. OurBigBook Web topics demo. Source. - local editing: you can store all your personal knowledge base content locally in a plaintext markup format that can be edited locally and published either:This way you can be sure that even if OurBigBook.com were to go down one day (which we have no plans to do as it is quite cheap to host!), your content will still be perfectly readable as a static site.

- to OurBigBook.com to get awesome multi-user features like topics and likes

- as HTML files to a static website, which you can host yourself for free on many external providers like GitHub Pages, and remain in full control

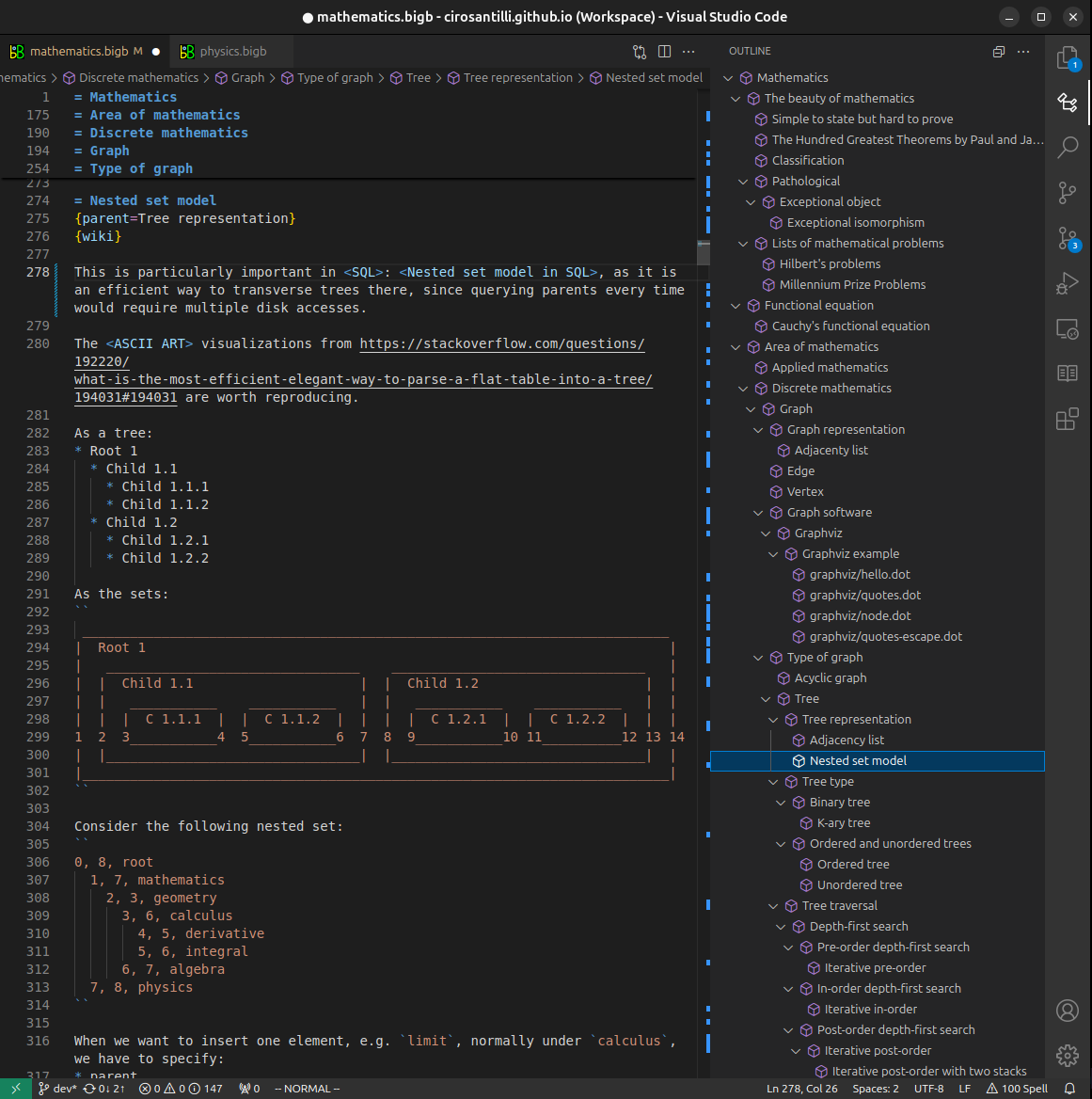

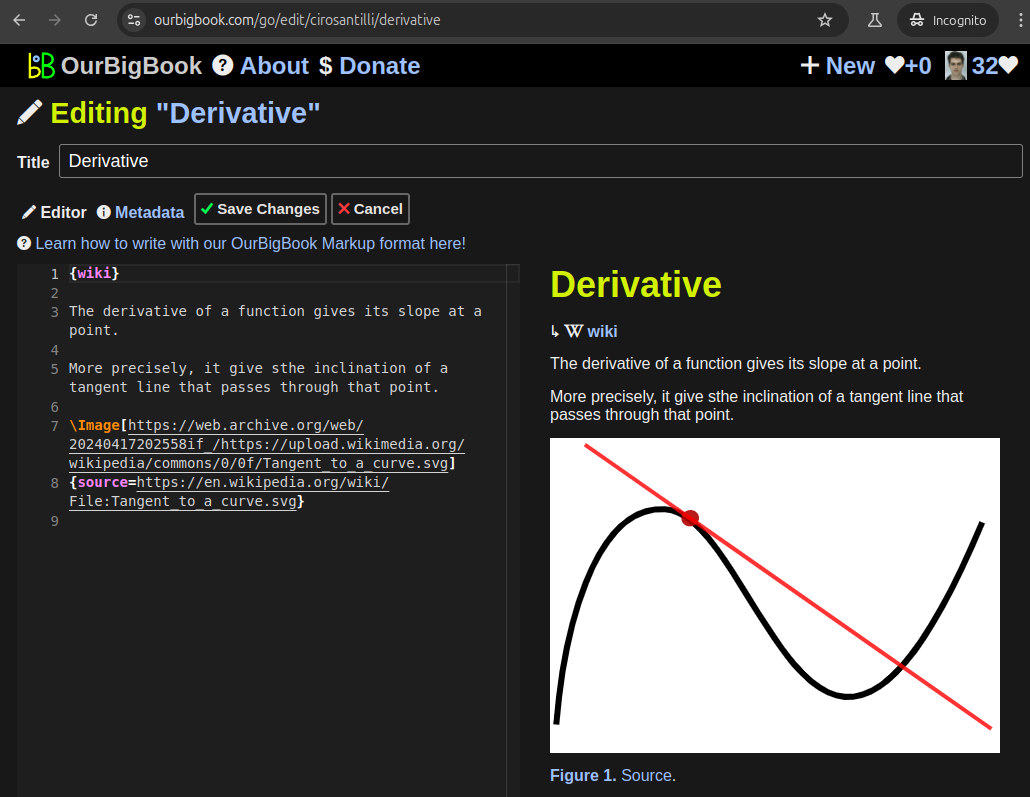

Figure 3. Visual Studio Code extension installation.Figure 4. Visual Studio Code extension tree navigation.Figure 5. Web editor. You can also edit articles on the Web editor without installing anything locally.Video 3. Edit locally and publish demo. Source. This shows editing OurBigBook Markup and publishing it using the Visual Studio Code extension.Video 4. OurBigBook Visual Studio Code extension editing and navigation demo. Source. - Infinitely deep tables of contents:

All our software is open source and hosted at: github.com/ourbigbook/ourbigbook

Further documentation can be found at: docs.ourbigbook.com

Feel free to reach our to us for any help or suggestions: docs.ourbigbook.com/#contact