A library and information scientist is a professional who specializes in the organization, management, and dissemination of information resources within libraries and other information-related settings. Their work involves various tasks related to the acquisition, cataloging, storage, retrieval, and preservation of information, as well as providing access to it for users. Key responsibilities of a library and information scientist may include: 1. **Collection Development**: Selecting, acquiring, and managing information resources, including books, journals, databases, and digital content.

As of my last update in October 2023, Natasha Devroye is not a widely recognized public figure, historical figure, or topic that has substantial information available. It's possible that she could be a private individual, a lesser-known professional, or a figure in a specific niche or community.

Peter Gács is a Hungarian-American computer scientist known for his contributions to various fields, including computational biology, computer science, and information theory. His work often involves topics such as algorithm design, complexity theory, and the mathematical foundations of computer science. He has published numerous papers and has been influential in the development of theoretical frameworks in these areas.

Fourier-transform infrared spectroscopy (FTIR) is an analytical technique used to obtain the infrared spectrum of absorption or emission of a solid, liquid, or gas. It is widely employed in chemistry, material science, and various fields to identify and characterize substances based on their molecular vibrations. ### Key Features of FTIR: 1. **Principle**: FTIR works on the principle that different molecules absorb specific frequencies of infrared light to produce vibrational transitions.

Fourier Transform Infrared Spectroscopy (FTIR) is a powerful analytical technique widely used in geology for various applications. Here are some of the primary applications of FTIR in geological studies: 1. **Mineral Identification**: FTIR is extensively used to identify and characterize minerals through their specific absorption bands. Different minerals exhibit unique spectral signatures, allowing for precise identification. 2. **Clay Mineral Analysis**: FTIR is particularly useful in the study of clay minerals, which have complex structures.

Infrared Nanospectroscopy, often referred to as AFM-IR (Atomic Force Microscopy-Infrared Spectroscopy), is a technique that combines atomic force microscopy (AFM) with infrared (IR) spectroscopy to provide spatially resolved chemical information at the nanoscale. This innovative approach enables researchers to study the chemical composition and properties of materials with high spatial resolution, typically at the nanoscale level, which is much finer than conventional IR spectroscopy techniques.

Libration in the context of molecular chemistry refers to a type of molecular motion, often associated with the oscillatory behavior of atoms or groups within a molecule. This motion usually involves small oscillations around an equilibrium position rather than large-scale rotations or translations. In many cases, libration is observed in large or complex organic molecules, especially those with flexible structures, where certain parts of the molecule can move relative to one another.

The term "unipotent" can refer to a few different contexts in mathematics, particularly in linear algebra and algebraic groups, and in biology.

Design fiction is a concept and practice that combines elements of design, storytelling, and speculative thinking to explore future scenarios, ideas, and technologies. It often involves creating tangible artifacts, narratives, or visual representations that provoke thought and discussion about possible futures, innovations, and their implications on society, culture, and the environment.

Narrative inquiry is a research methodology and approach that explores how people make sense of their experiences through storytelling. It emphasizes the ways in which individuals construct meaning and identity through narratives, focusing on personal stories as vital sources of knowledge. This approach is often used in fields such as education, psychology, sociology, and anthropology.

Philosophical inquiry is the process of exploring fundamental questions about existence, knowledge, values, reason, mind, and language through critical thinking, logical analysis, and systematic reflection. It involves examining and questioning beliefs, assumptions, and concepts to gain a deeper understanding of various philosophical issues. Philosophical inquiry can take various forms, including: 1. **Critical Analysis**: Evaluating arguments and ideas to determine their validity and soundness.

A **magic constant** is the sum of the numbers in any row, column, or diagonal of a magic square. A magic square is a grid arrangement of distinct integers such that the sum of the numbers in each row, column, and both main diagonals is the same.

David Lang is an American composer and one of the influential figures in contemporary classical music. He was born on January 8, 1957, in Los Angeles, California. Lang is known for his diverse range of musical works, including orchestral pieces, chamber music, and vocal compositions. He is also a co-founder of the music collective Bang on a Can, which promotes experimental and avant-garde music.

The Wolf Prize is awarded annually in several fields, including mathematics, physics, chemistry, and more. Various winners have been affiliated with the Institute for Advanced Study (IAS) in Princeton, New Jersey. While I cannot provide a comprehensive and up-to-date list, I can mention some notable winners who have been associated with the IAS as of my last knowledge update in October 2023: 1. **John Nash** - Awarded the Wolf Prize in Mathematics in 1986.

The National Humanities Center (NHC) is an independent institute located in the United States that is dedicated to advancing research in the humanities. Founded in 1978, it is one of the leading organizations in promoting scholarship in areas such as history, literature, philosophy, and cultural studies. The Center provides support for researchers through fellowships, resources, and various programs aimed at fostering interdisciplinary research and collaboration among scholars in the humanities.

Robert Kirby-Harris is not widely recognized in mainstream media or prominent historical contexts, so there may be limited public information about him. If you are looking for a specific individual, it may help to provide additional context, such as their profession or relevance to a certain field. It’s also possible that he may be a private individual or a figure in a specialized area.

Harry Leinweber may refer to an individual's name, but without additional context, it's difficult to provide specific information. It’s possible he could be a public figure, a scholar, or someone known in a particular field.

Martin Copley is a name that might refer to various individuals; however, one notable Martin Copley is a British conservationist and wildlife filmmaker known for his work in promoting and documenting wildlife and environmental issues. He has made contributions to wildlife conservation and has been involved with several projects focused on preserving natural habitats and species.

A binary sequence is a sequence of numbers where each number is either a 0 or a 1. These sequences are fundamental in various fields, particularly in computer science and digital electronics, as they represent the most basic form of data storage and processing. ### Characteristics of Binary Sequences: 1. **Composition**: Each element of the sequence can take on one of two possible values: 0 or 1.

Pinned article: Introduction to the OurBigBook Project

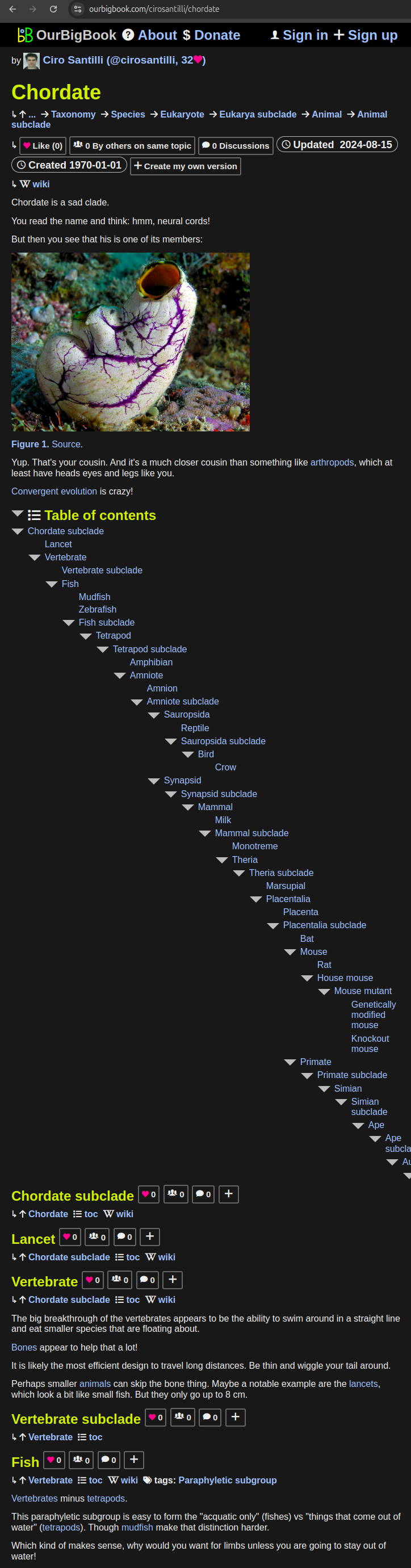

Welcome to the OurBigBook Project! Our goal is to create the perfect publishing platform for STEM subjects, and get university-level students to write the best free STEM tutorials ever.

Everyone is welcome to create an account and play with the site: ourbigbook.com/go/register. We belive that students themselves can write amazing tutorials, but teachers are welcome too. You can write about anything you want, it doesn't have to be STEM or even educational. Silly test content is very welcome and you won't be penalized in any way. Just keep it legal!

Intro to OurBigBook

. Source. We have two killer features:

- topics: topics group articles by different users with the same title, e.g. here is the topic for the "Fundamental Theorem of Calculus" ourbigbook.com/go/topic/fundamental-theorem-of-calculusArticles of different users are sorted by upvote within each article page. This feature is a bit like:

- a Wikipedia where each user can have their own version of each article

- a Q&A website like Stack Overflow, where multiple people can give their views on a given topic, and the best ones are sorted by upvote. Except you don't need to wait for someone to ask first, and any topic goes, no matter how narrow or broad

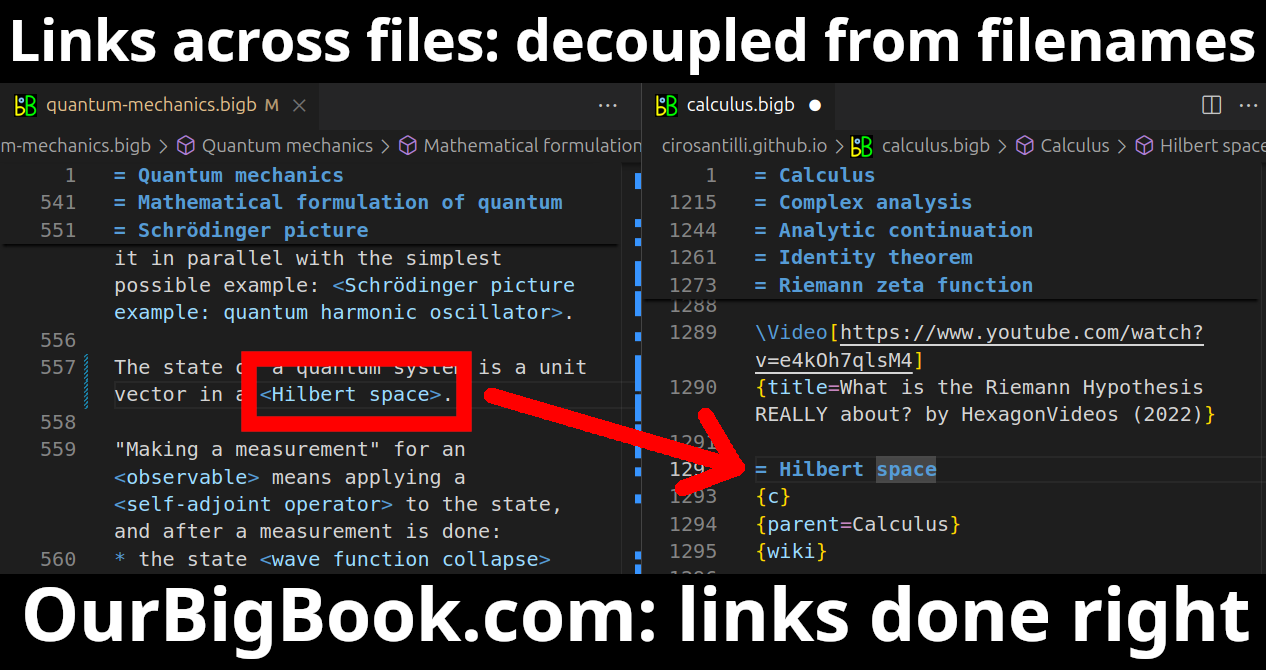

This feature makes it possible for readers to find better explanations of any topic created by other writers. And it allows writers to create an explanation in a place that readers might actually find it.Figure 1. Screenshot of the "Derivative" topic page. View it live at: ourbigbook.com/go/topic/derivativeVideo 2. OurBigBook Web topics demo. Source. - local editing: you can store all your personal knowledge base content locally in a plaintext markup format that can be edited locally and published either:This way you can be sure that even if OurBigBook.com were to go down one day (which we have no plans to do as it is quite cheap to host!), your content will still be perfectly readable as a static site.

- to OurBigBook.com to get awesome multi-user features like topics and likes

- as HTML files to a static website, which you can host yourself for free on many external providers like GitHub Pages, and remain in full control

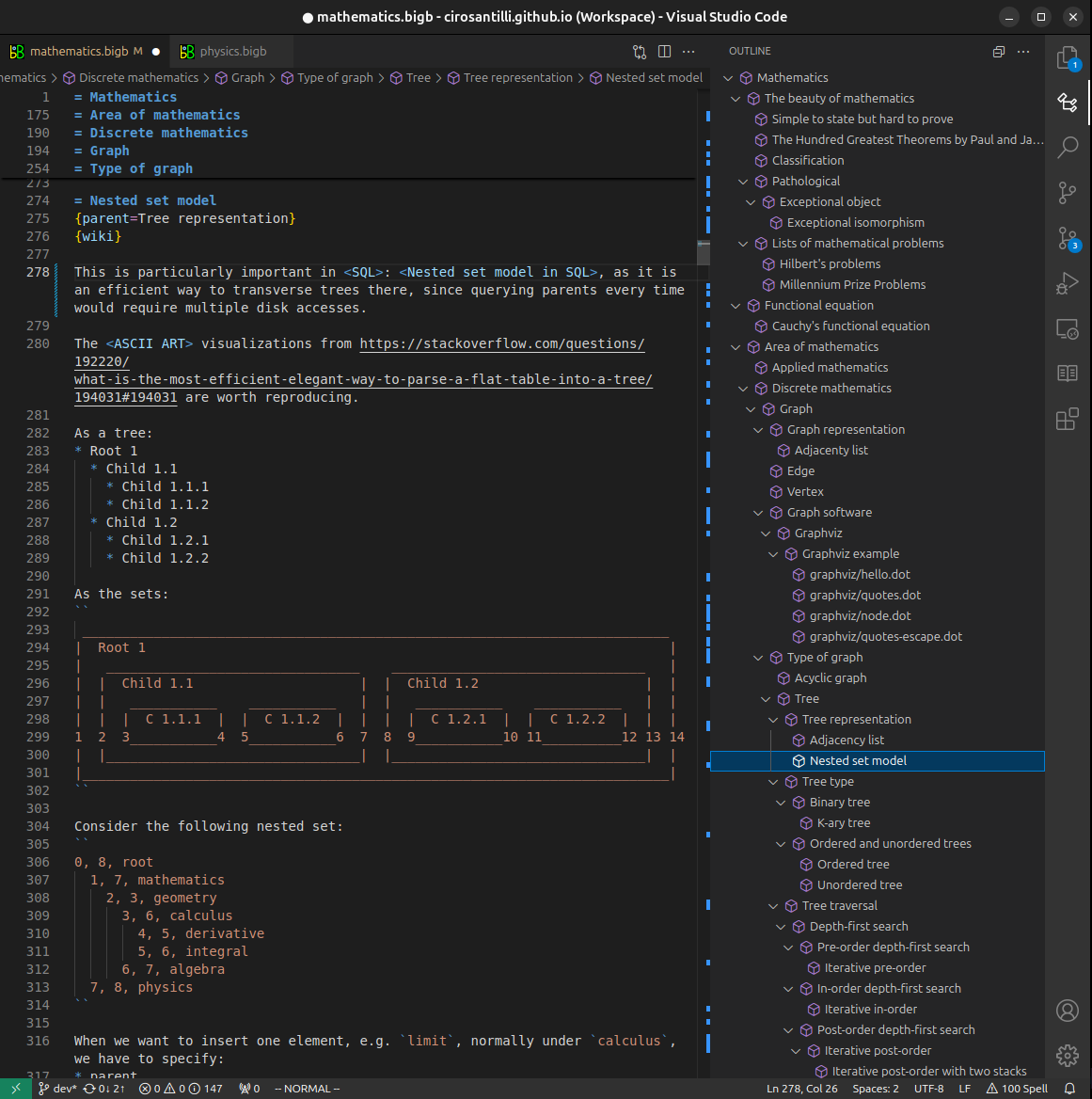

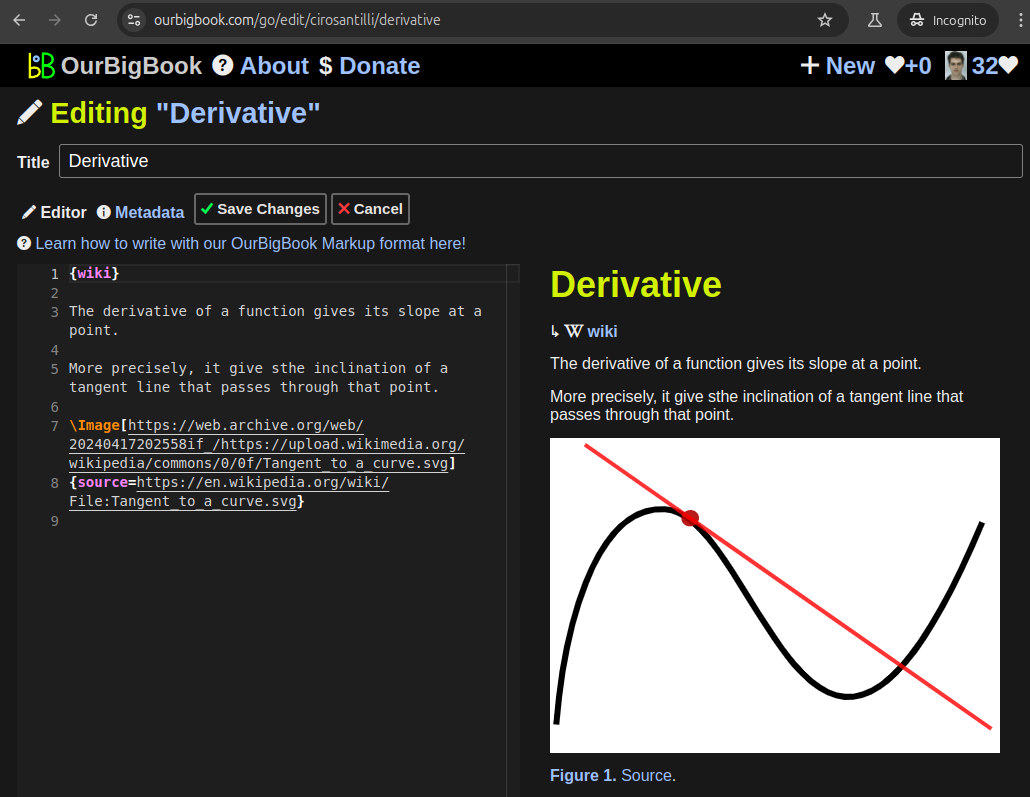

Figure 3. Visual Studio Code extension installation.Figure 4. Visual Studio Code extension tree navigation.Figure 5. Web editor. You can also edit articles on the Web editor without installing anything locally.Video 3. Edit locally and publish demo. Source. This shows editing OurBigBook Markup and publishing it using the Visual Studio Code extension.Video 4. OurBigBook Visual Studio Code extension editing and navigation demo. Source. - Infinitely deep tables of contents:

All our software is open source and hosted at: github.com/ourbigbook/ourbigbook

Further documentation can be found at: docs.ourbigbook.com

Feel free to reach our to us for any help or suggestions: docs.ourbigbook.com/#contact