GDB Dashboard Updated 2025-07-16

The Oxford Solid State Basics Updated 2025-07-16

x86 Paging Tutorial PAE and PSE page table schemes Updated 2025-07-16

If either PAE and PSE are active, different paging level schemes are used:

- no PAE and no PSE:

10 | 10 | 12 - no PAE and PSE:

10 | 22.22 is the offset within the 4Mb page, since 22 bits address 4Mb. - PAE and no PSE:

2 | 9 | 9 | 12The design reason why 9 is used twice instead of 10 is that now entries cannot fit anymore into 32 bits, which were all filled up by 20 address bits and 12 meaningful or reserved flag bits.The reason is that 20 bits are not enough anymore to represent the address of page tables: 24 bits are now needed because of the 4 extra wires added to the processor.Therefore, the designers decided to increase entry size to 64 bits, and to make them fit into a single page table it is necessary reduce the number of entries to 2^9 instead of 2^10. - PAE and PSE:

2 | 9 | 21

Stereochemistry Updated 2025-07-16

United States Armed Forces Updated 2025-07-16

Charity school Updated 2025-07-16

Year 3 of the physics course of the University of Oxford Updated 2025-07-16

Legendre's three-square theorem Updated 2025-07-16

Cirodance Updated 2025-07-16

During his teenage years, Ciro created an innovative new dance style combining elements of the various corporal practices that he studied a bit of across the years:

- Kung Fu/Taichi

- Brazilian Axé and Capoeira

- Breakdance

- Yoga

- Modern dance

Ciro later called this style Cirodance.

Ciro's legendary dance style was famous during his university years, when Ciro would go to parties and dance like made while mostly unsuccessfully trying to woo girls.

Ciro has always been critical of dancing conditions in University parties, where people would always be cramped up doing boring non-creative moves. Rather, Ciro would go to to the edges of the dance floor to have enough space for his amazing moves. There is a perhaps a parallel between such tendencies and Ciro's highly innovative personality. Also perhaps being cramped would have helped wooing said girls.

Ciro later quit dancing, to a large extent because it is too hard to find suitable dancing locations outside: Europe is too cold much of the year, also ground conditions have to be perfect, and no patience to book a dance room somewhere. Kid's playgrounds are ideal, but Ciro is afraid of dancing there because kids parent's would freak out.

Therefore, all evidence of Cirodance seems to have disappeared into the depths of the Internet. There used to be a notorious video on YouTube from around June 2010 entitled "A Piriguete da Poli !!" ("Poli's bitch" in Portuguese) with comment "Sem comentarios... foi a atraçao da cervejada" (No comments... was the main attraction of the beer party) dancing the Piriguete by MC Papo Brazilian Funk carioca song. But the video was removed at some point, they were likely afraid of getting sued, the URL was www.youtube.com/watch?v=T969azGjIeE as shown at www.facebook.com/cirosantilli/posts/133333123357495, but this was before Ciro noticed that every good thing on the web goes down and became an obsessive web archiver. But in any case, the title gives an idea of the amazing style of Ciro's furor poeticus Axé performance on that day. If the video owner ever reads this message, please please restore the video, or send Ciro a copy. TODO: which channel was it on? Knowing that Ciro would be able to try and contact them.

One legendary episode linked to Cirodance was when Ciro was living in Paris and jobless around 2014 (but not destitute as he leached from his girlfriend). Cirodance was his main physical activity at the time, and Place de la République, where the skateboarders hung out due to the perfect wide concrete floor and relatively close to Bastille where Ciro lived, was the perfect place for it. One cold dark winter evening, Ciro was practicing Cirodance with his headphones and crappy clothes (dirty public square floor, remember), when someone took him for a homeless person and offered him a bowl of soup! It must be said that Place de la République had many events of giving food to the poor. Ciro was a bit stunned, declined, and continued dancing. And so that was the day when a prestigious Polytechnicien was mistaken for a homeless person. And Ciro liked that.

As of 2021, Googling "cirodance" leads to www.youtube.com/watch?v=tyvv4ddL2so "Ciro Dance" in which comedian "Ciro Priello" (no Wikipedia page at the time) participates in a comedy show with a "silly dance" (TODO this likely has a name) described in the comments as:

Guqin bibliography Updated 2025-07-16

Bibliography:

U.S. state Updated 2025-07-16

Geologic time scale hierarchy Updated 2025-07-16

Guzheng Updated 2025-07-16

San Francisco Updated 2025-07-16

x86 Paging Tutorial Page faults Updated 2025-07-16

When an exception happens, the CPU jumps to an address that the OS had previously registered as the fault handler. This is usually done at boot time by the OS.

This could happen for example due to a programming error:but there are cases where it is not a bug, for example in Linux when:

int *is = malloc(1);

is[2] = 1;- the program wants to increase its stack.

- the page was swapped to disk.The OS will need to do some work behind the processes back to get the page back into RAM.

History of radio Updated 2025-07-16

Journey to the West (1986 TV series) Updated 2025-07-16

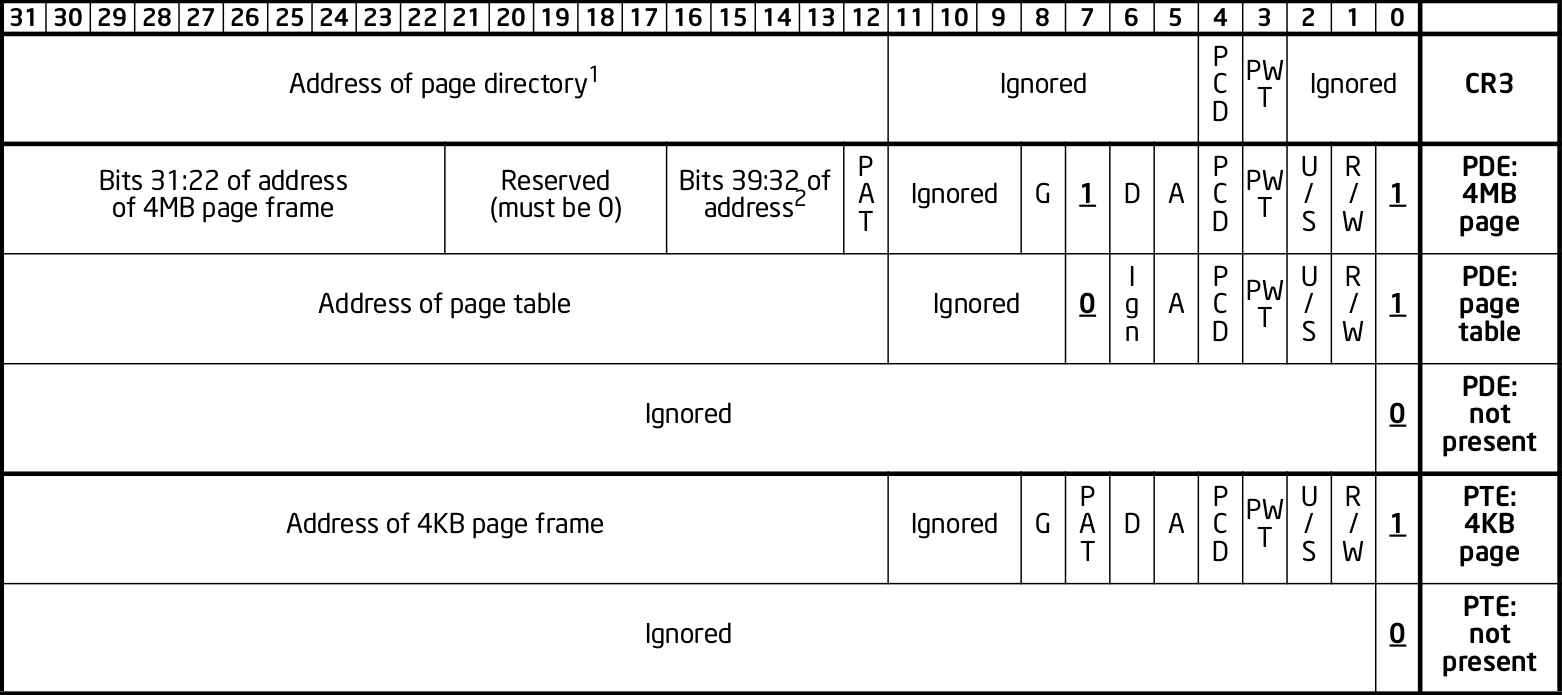

x86 Paging Tutorial Page table entries Updated 2025-07-16

The exact format of table entries is fixed by the hardware.

The page table is then an array of

struct.On this simplified example, the page table entries contain only two fields:so in this example the hardware designers could have chosen the size of the page table to b

bits function

----- -----------------------------------------

20 physical address of the start of the page

1 present flag21 instead of 32 as we've used so far.All real page table entries have other fields, notably fields to set pages to read-only for Copy-on-write. This will be explained elsewhere.

It would be impractical to align things at 21 bits since memory is addressable by bytes and not bits. Therefore, even in only 21 bits are needed in this case, hardware designers would probably choose 32 to make access faster, and just reserve bits the remaining bits for later usage. The actual value on x86 is 32 bits.

Here is a screenshot from the Intel manual image "Formats of CR3 and Paging-Structure Entries with 32-Bit Paging" showing the structure of a page table in all its glory: Figure 1. "x86 page entry format".

The fields are explained in the manual just after.

Aufbau principle Updated 2025-07-16

Boring rule that says that less energetic atomic orbitals are filled first.

Much more interesting is actually determining that order, which the Madelung energy ordering rule is a reasonable approximation to.

x86 Paging Tutorial Process memory layout Updated 2025-07-16

For each process, the virtual address space looks like this:

------------------ 2^32 - 1

Stack (grows down)

v v v v v v v v v

------------------

(unmapped)

------------------ Maximum stack size.

(unmapped)

-------------------

mmap

-------------------

(unmapped)

-------------------

^^^^^^^^^^^^^^^^^^^

brk (grows up)

-------------------

BSS

-------------------

Data

-------------------

Text

-------------------

------------------- 0The kernel maintains a list of pages that belong to each process, and synchronizes that with the paging.

If the program accesses memory that does not belong to it, the kernel handles a page-fault, and decides what to do:

When an ELF file is loaded by the kernel to start a program with the

exec system call, the kernel automatically registers text, data, BSS and stack for the program.The

brk and mmap areas can be modified by request of the program through the brk and mmap system calls. But the kernel can also deny the program those areas if there is not enough memory.brk and mmap can be used to implement malloc, or the so called "heap".mmap is also used to load dynamically loaded libraries into the program's memory so that it can access and run it.Stack allocation: stackoverflow.com/questions/17671423/stack-allocation-for-process

Calculating exact addresses Things are complicated by:

- Address Space Layout Randomization.

- the fact that environment variables, CLI arguments, and some ELF header data take up initial stack space: unix.stackexchange.com/questions/145557/how-does-stack-allocation-work-in-linux/239323#239323

Why the text does not start at 0: stackoverflow.com/questions/14795164/why-do-linux-program-text-sections-start-at-0x0804800-and-stack-tops-start-at-0

There are unlisted articles, also show them or only show them.