Moodle instance of the Mathematical Institute of the University of Oxford.

Has a mixture of open access and closed access. But at least it can have open access unlike the in-house systems such as Canvas where everything is necessarily paywalled!

Sometimes things appear open but don't show any meaningful content if you are not logged in, which is annoying.

But at least it gives a clear public course list, thing that certain departments (cough Department of Physics of the University of Oxford cough).

The organization is a bit crap, when you expand e.g. C Michaelmas term it shows nothing, just a search.

The way to go is via the year year categories e.g. "Year 2022-23": courses.maths.ox.ac.uk/course/index.php?categoryid=734. Term splitting is annoying, but one can stand it.

TODO confirm URL: oxfordgossip.co.uk ? An archive from 2005 when it was hottest: web.archive.org/web/20051204033916/http://www.oxfordgossip.co.uk/new/

TODO spiciest posts ever?

Like the U.S.' summer term.

E-learning system prior to Canvas: weblearn.ox.ac.uk/portal. Appears fully custom and closed source?

Similar to a college, but led by religious denomination leaders rather than fellows.

For students (who are paying for the university to start with...), they will not claim tutorials linked to courses. But a tutorial that shows university laboratories, it is unclear: www.ox.ac.uk/students/academic/guidance/intellectual-property (archive) This likely includes graduate students, who are also not paid by the university.

For faculty, the university owns everything it seems, to be confirmed.

Maximum current that can flow across a Josephson junction, as can be directly seen from the Josephson equations.

Is a fixed characteristic value of the physical construction of the junction.

Session reports of the Royal Prussian Academy of Sciences at Berlin by  Ciro Santilli 40 Updated 2025-07-16

Ciro Santilli 40 Updated 2025-07-16

Publications by the Prussian Academy of Sciences.

Links to their publications: de.wikisource.org/wiki/Sitzungsberichte_der_K%C3%B6niglich_Preu%C3%9Fischen_Akademie_der_Wissenschaften_zu_Berlin

Notable papers:

Does this contain any structured data? E.g. can you list all papers by a given author besides just searching and hoping there are no homonyms?

Real hardware is for newbs. Real hardware is for newbs.

Tested on Ubuntu 23.10 we approximately follow instructions from: docs.zephyrproject.org/3.4.0/develop/getting_started/index.html stopping before the "Flash the sample" section, as we don't flash QEMU. We just run it.

sudo apt install --no-install-recommends git cmake ninja-build gperf \

ccache dfu-util device-tree-compiler wget \

python3-dev python3-pip python3-setuptools python3-tk python3-wheel xz-utils file \

make gcc gcc-multilib g++-multilib libsdl2-dev libmagic1 python3-pyelftools

python3 -m venv ~/zephyrproject/.venv

source ~/zephyrproject/.venv/bin/activate

pip install west

west init ~/zephyrproject

cd ~/zephyrproject

west update

west zephyr-export

cd ~

wget https://github.com/zephyrproject-rtos/sdk-ng/releases/download/v0.16.1/zephyr-sdk-0.16.1_linux-x86_64.tar.xz

tar xvf zephyr-sdk-0.16.1_linux-x86_64.tar.xz

cd zephyr-sdk-0.16.1

./setup.shThe installation procedure install all compiler toolchains for us, so we can then basically compile for any target. It also fetches the latest Git source code of Zephyr under:

~/zephyrproject/zephyrThe "most default" blinky hello world example which blinks an LED is a bit useless for us because QEMU doesn't have LEDs, so instead we are going to use one of the UART examples which will print characters we can see on QEMU stdout.

Let's start with the hello world example on an x86 target:and it outputs:The

cd ~/zephyrproject/zephyr

west build -b qemu_x86 samples/hello_world -t runHello World! qemu_x86qemu_x64 on the output comes from the CONFIG_BOARD macro github.com/zephyrproject-rtos/zephyr/blob/c15ff103001899ba0321b2c38013d1008584edc0/samples/hello_world/src/main.c#L11#include <zephyr/kernel.h>

int main(void)

{

printk("Hello World! %s\n", CONFIG_BOARD);

return 0;

}The

qemu_x86 board is documented at: docs.zephyrproject.org/3.4.0/boards/x86/qemu_x86/doc/index.htmlYou can also first

cd into the directory that you want to build in to avoid typing samples/hello_world all the time:cd ~/zephyrproject/zephyr/samples/hello_world

zephyr west build -b qemu_x86 -t runYou can also build and run separately with:

west build -b qemu_x86

west build -t runAnother important option is:But note that it does not modify your

west build -t menuconfigprj.conf automatically for you.Let's try on another target:and same output, but on a completely different board! The

rm -rf build

zephyr west build -b qemu_cortex_a53 -t runqemu_cortex_a53 board is documented at: docs.zephyrproject.org/3.4.0/boards/arm64/qemu_cortex_a53/doc/index.htmlThe list of all examples can be seen under:which for example contains:

ls ~/zephyrproject/zephyr/sampleszephyrproject/zephyr/samples/hello_worldSo run another sample simply select it, e.g. to run

zephyrproject/zephyr/samples/synchronization:west build -b qemu_cortex_a53 samples/synchronization -t runTheory that gases are made up of a bunch of small billiard balls that don't interact with each other.

This theory attempts to deduce/explain properties of matter such as the equation of state in terms of classical mechanics.

Pinned article: Introduction to the OurBigBook Project

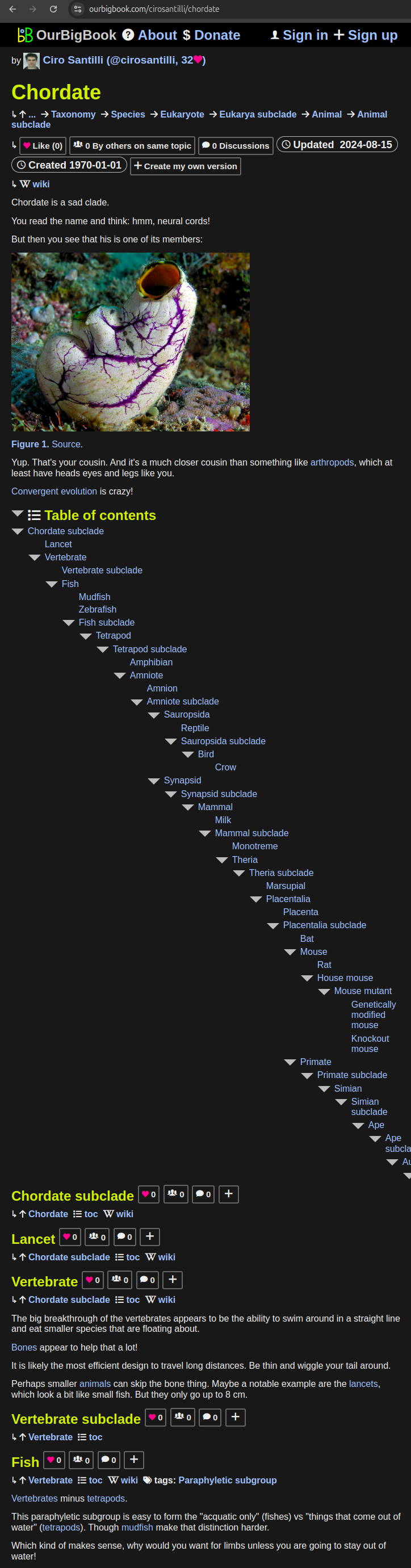

Welcome to the OurBigBook Project! Our goal is to create the perfect publishing platform for STEM subjects, and get university-level students to write the best free STEM tutorials ever.

Everyone is welcome to create an account and play with the site: ourbigbook.com/go/register. We belive that students themselves can write amazing tutorials, but teachers are welcome too. You can write about anything you want, it doesn't have to be STEM or even educational. Silly test content is very welcome and you won't be penalized in any way. Just keep it legal!

Intro to OurBigBook

. Source. We have two killer features:

- topics: topics group articles by different users with the same title, e.g. here is the topic for the "Fundamental Theorem of Calculus" ourbigbook.com/go/topic/fundamental-theorem-of-calculusArticles of different users are sorted by upvote within each article page. This feature is a bit like:

- a Wikipedia where each user can have their own version of each article

- a Q&A website like Stack Overflow, where multiple people can give their views on a given topic, and the best ones are sorted by upvote. Except you don't need to wait for someone to ask first, and any topic goes, no matter how narrow or broad

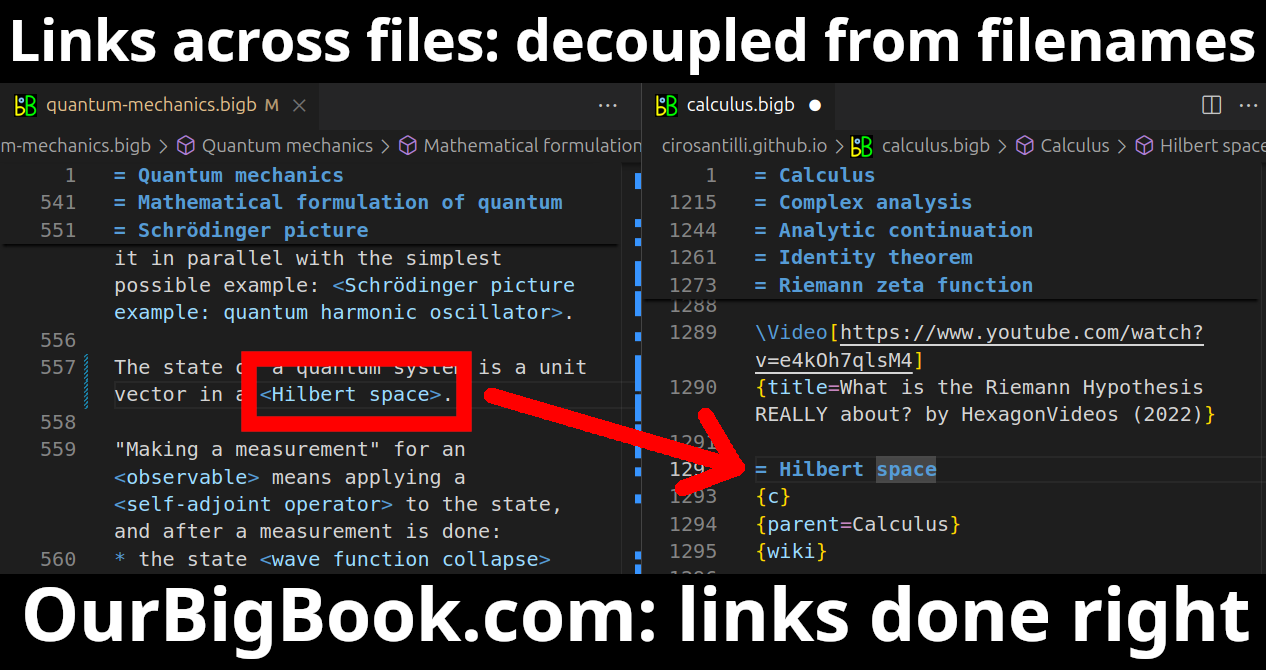

This feature makes it possible for readers to find better explanations of any topic created by other writers. And it allows writers to create an explanation in a place that readers might actually find it.Figure 1. Screenshot of the "Derivative" topic page. View it live at: ourbigbook.com/go/topic/derivativeVideo 2. OurBigBook Web topics demo. Source. - local editing: you can store all your personal knowledge base content locally in a plaintext markup format that can be edited locally and published either:This way you can be sure that even if OurBigBook.com were to go down one day (which we have no plans to do as it is quite cheap to host!), your content will still be perfectly readable as a static site.

- to OurBigBook.com to get awesome multi-user features like topics and likes

- as HTML files to a static website, which you can host yourself for free on many external providers like GitHub Pages, and remain in full control

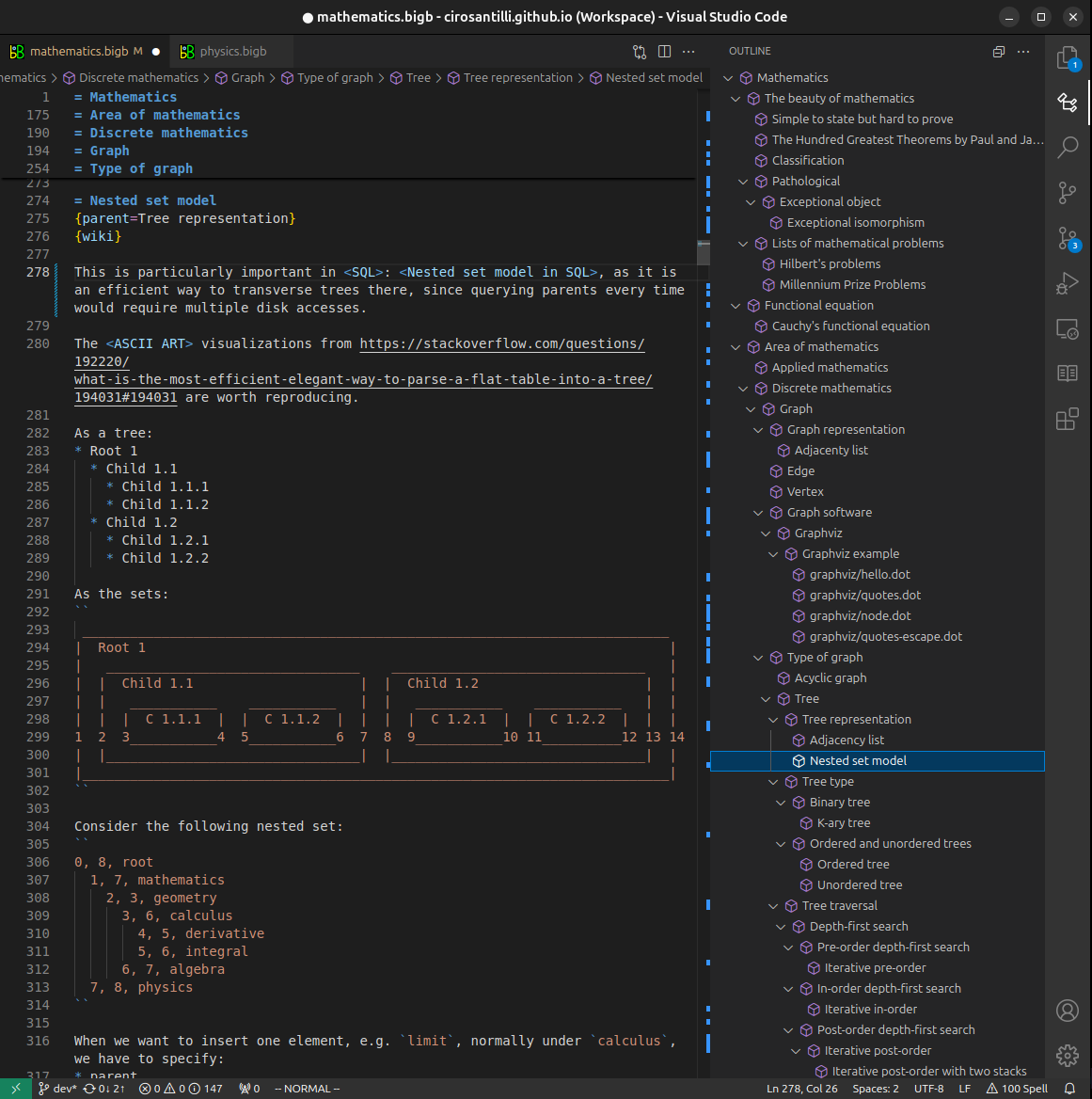

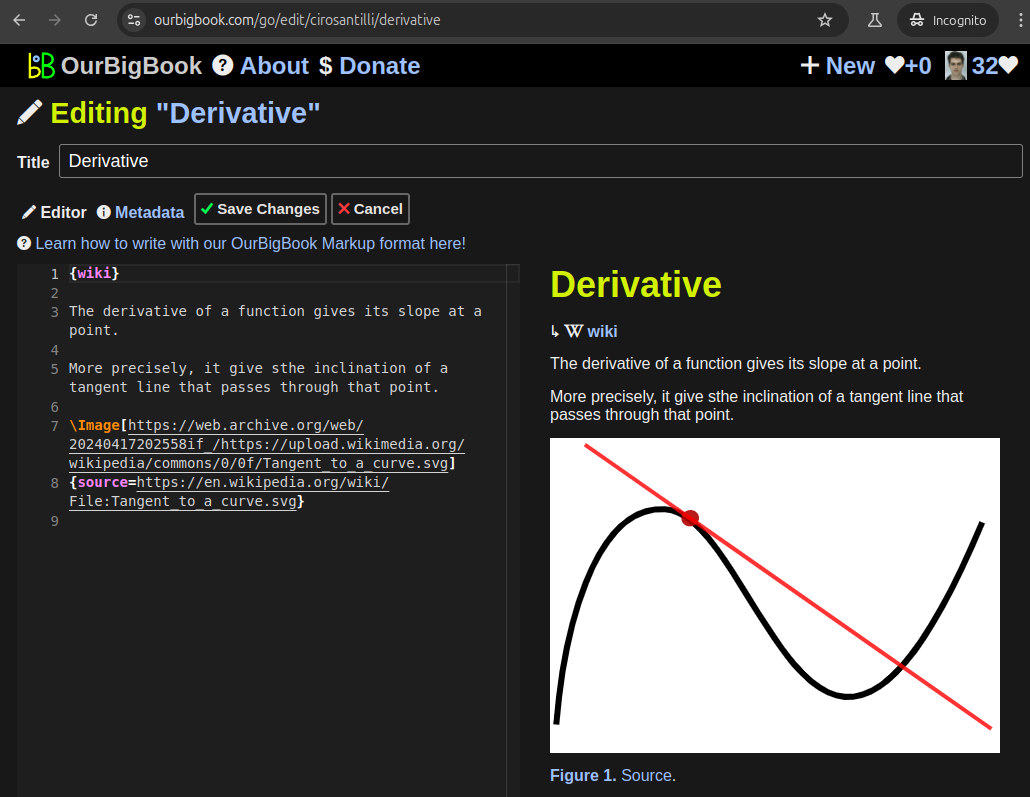

Figure 3. Visual Studio Code extension installation.Figure 4. Visual Studio Code extension tree navigation.Figure 5. Web editor. You can also edit articles on the Web editor without installing anything locally.Video 3. Edit locally and publish demo. Source. This shows editing OurBigBook Markup and publishing it using the Visual Studio Code extension.Video 4. OurBigBook Visual Studio Code extension editing and navigation demo. Source. - Infinitely deep tables of contents:

All our software is open source and hosted at: github.com/ourbigbook/ourbigbook

Further documentation can be found at: docs.ourbigbook.com

Feel free to reach our to us for any help or suggestions: docs.ourbigbook.com/#contact