Thomas Young (1773–1829) was an English polymath who made significant contributions to various fields including physics, physiology, and linguistics. He is perhaps best known for his work in the field of optics and is widely recognized for his formulation of the wave theory of light. One of Young's most famous experiments is the double-slit experiment, which demonstrated that light can exhibit characteristics of both waves and particles.

William Parkinson Wilson does not appear to be a widely recognized figure or concept based on the information available up to October 2023. It is possible he could be a private individual or an emerging figure in a specialized field.

Auguste Bravais (1811–1863) was a French physicist and botanist best known for his work in crystallography. He is most famous for developing the concept of Bravais lattices, which are a set of distinct lattice structures that describe how atoms are arranged in a crystalline solid. Bravais lattices help categorize crystals based on their symmetry and the arrangement of their constituent particles in three-dimensional space.

As of my last knowledge update in October 2021, Claire Berger may refer to various individuals or contexts, but one prominent figure associated with that name is a French mathematician known for her work in mathematics education and advocacy for women in STEM fields.

Georges Sagnac was a French physicist best known for his work in the field of optics and his experiments related to the theory of relativity. Born on June 14, 1869, Sagnac is particularly famous for the Sagnac effect, which he demonstrated in 1913. The Sagnac effect involves the observation that a rotating interferometer produces a measurable phase shift in light beams that travel in opposite directions around a closed loop.

Joseph Zyss is a prominent physicist known for his contributions to the fields of optics and photonics. He has been involved in research related to nonlinear optics, laser technology, and the development of optical devices and systems. Zyss has also played a significant role in academic and research institutions, contributing to advancements in optical materials and technologies.

As of my last update in October 2023, "Lucien Vidi" does not refer to a widely recognized figure, concept, or term in popular culture, literature, science, or any significant field. It's possible that it could be a name of a person, an emerging topic, or something specific to a local context not well-documented in widely available sources.

Mathias Fink is a noted French physicist known for his contributions to the field of ultrasound and applied acoustics. He is particularly recognized for his work in developing imaging techniques and methods that enhance the understanding of structures and materials using ultrasonic waves. His research often bridges the gap between fundamental physics and practical applications in medical imaging, non-destructive testing, and other fields where ultrasound is utilized. Fink has published numerous scientific papers and has been involved in various academic and research institutions.

As of my last knowledge update in October 2021, Karl Heinz Bennemann does not appear to be a widely recognized figure in politics, science, art, or other prominent fields. It's possible that he could be a lesser-known individual, a local figure, or a character in a specific context that hasn't gained widespread recognition. If you have a specific area or context in mind, such as a particular field (e.g.

Werner Jacobi is a German-American composer and conductor, known primarily for his work in contemporary classical music. However, the name Werner Jacobi may also refer to other individuals, such as scientists or figures from different fields, depending on the context.

Diana Deutsch is a renowned psychologist known for her research in the fields of psychology and music perception. She is particularly recognized for her work on auditory illusions and the intersection of music and cognitive psychology. Deutsch has conducted numerous studies that investigate how individuals perceive sound, including the famous "scale illusion" and the "octave illusion," which demonstrate interesting aspects of auditory processing.

Gerhard M. Sessler is a prominent physicist and electrical engineer known for his contributions to the field of acoustics and transducer technology. He is particularly recognized for his work on electret microphones and piezoelectric sensors. Sessler has made significant advancements in the design and application of various types of microphones, enhancing their performance and usability in a variety of electronic devices. His research has implications in telecommunications, audio engineering, and various other fields where sound capture and manipulation are important.

Robert Remez is a prominent figure in the field of psychology, particularly known for his research on language perception and the cognitive processes involved in speech and language understanding. He has conducted studies that explore how humans process spoken language, including phenomena such as speech perception and the integration of contextual information. Remez has contributed to our understanding of how people detect and interpret speech sounds, even in noisy environments or when speech is distorted.

"Discoverers of moons" refers to the individuals or groups who have identified and named the natural satellites (moons) of planets in our solar system.

"Discoveries" by Andrew C. Becker is a work that delves into the themes of exploration, innovation, and the pursuit of knowledge. While specific details about the content or context of the work are not widely known, it may involve scientific exploration, personal journeys, or philosophical inquiries into what it means to make discoveries.

"Discoveries" by Attila Szing appears to be a work that I don’t have specific information about, as it may not be widely recognized in mainstream literature or media as of my last knowledge update in October 2023. If it's a recent publication or a lesser-known work, details might be limited or not available in common databases.

"Discoveries" by Celina Mikolajczak is a book that explores themes of personal growth, self-discovery, and the journey of understanding oneself and the world. Celina Mikolajczak often intertwines her experiences and insights in a way that resonates with readers who are seeking inspiration or reflection on their own life journeys. The book may delve into various topics such as resilience, overcoming challenges, and the importance of embracing one's identity and experiences.

"Discoveries" is a well-known art book by Cuno Hoffmeister, published in 1959. Cuno Hoffmeister was a German artist reminiscent of some abstract tendencies, and his works often explore themes of color and geometric forms. The book typically features a collection of his artworks along with essays that provide insights into his artistic philosophy and approach.

"Discoveries" by Don J. Wells is a work that explores various themes, concepts, or topics related to human experience, innovation, or personal growth. The specifics of the content can vary, as it may include insights based on the author's experiences, research, or reflections on discoveries in various fields.

Pinned article: Introduction to the OurBigBook Project

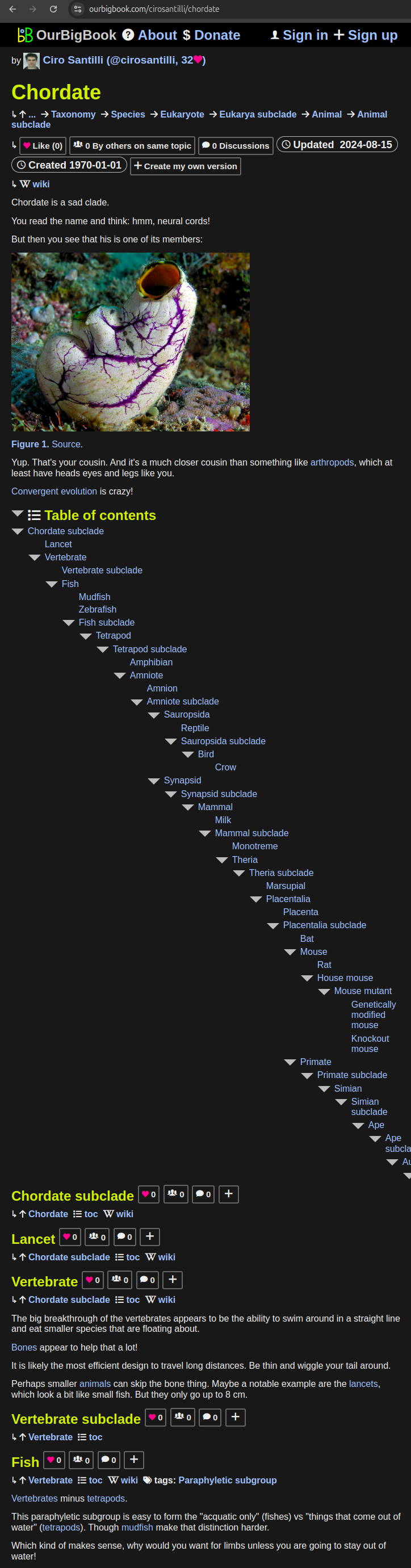

Welcome to the OurBigBook Project! Our goal is to create the perfect publishing platform for STEM subjects, and get university-level students to write the best free STEM tutorials ever.

Everyone is welcome to create an account and play with the site: ourbigbook.com/go/register. We belive that students themselves can write amazing tutorials, but teachers are welcome too. You can write about anything you want, it doesn't have to be STEM or even educational. Silly test content is very welcome and you won't be penalized in any way. Just keep it legal!

Intro to OurBigBook

. Source. We have two killer features:

- topics: topics group articles by different users with the same title, e.g. here is the topic for the "Fundamental Theorem of Calculus" ourbigbook.com/go/topic/fundamental-theorem-of-calculusArticles of different users are sorted by upvote within each article page. This feature is a bit like:

- a Wikipedia where each user can have their own version of each article

- a Q&A website like Stack Overflow, where multiple people can give their views on a given topic, and the best ones are sorted by upvote. Except you don't need to wait for someone to ask first, and any topic goes, no matter how narrow or broad

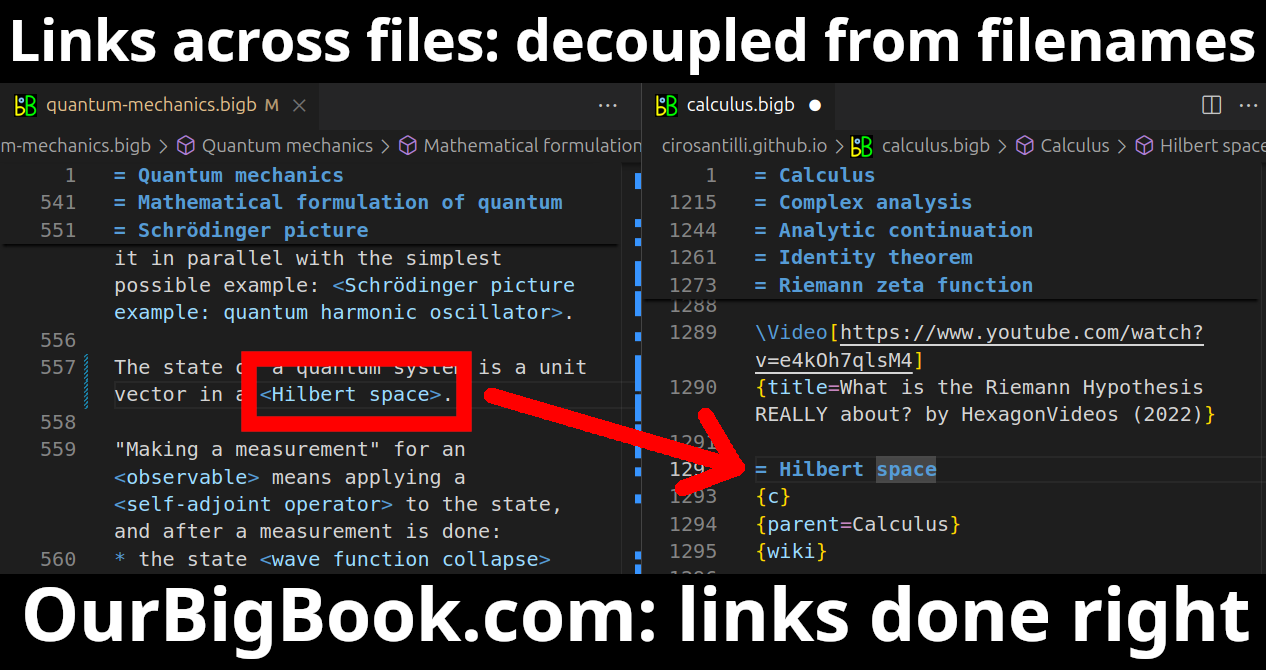

This feature makes it possible for readers to find better explanations of any topic created by other writers. And it allows writers to create an explanation in a place that readers might actually find it.Figure 1. Screenshot of the "Derivative" topic page. View it live at: ourbigbook.com/go/topic/derivativeVideo 2. OurBigBook Web topics demo. Source. - local editing: you can store all your personal knowledge base content locally in a plaintext markup format that can be edited locally and published either:This way you can be sure that even if OurBigBook.com were to go down one day (which we have no plans to do as it is quite cheap to host!), your content will still be perfectly readable as a static site.

- to OurBigBook.com to get awesome multi-user features like topics and likes

- as HTML files to a static website, which you can host yourself for free on many external providers like GitHub Pages, and remain in full control

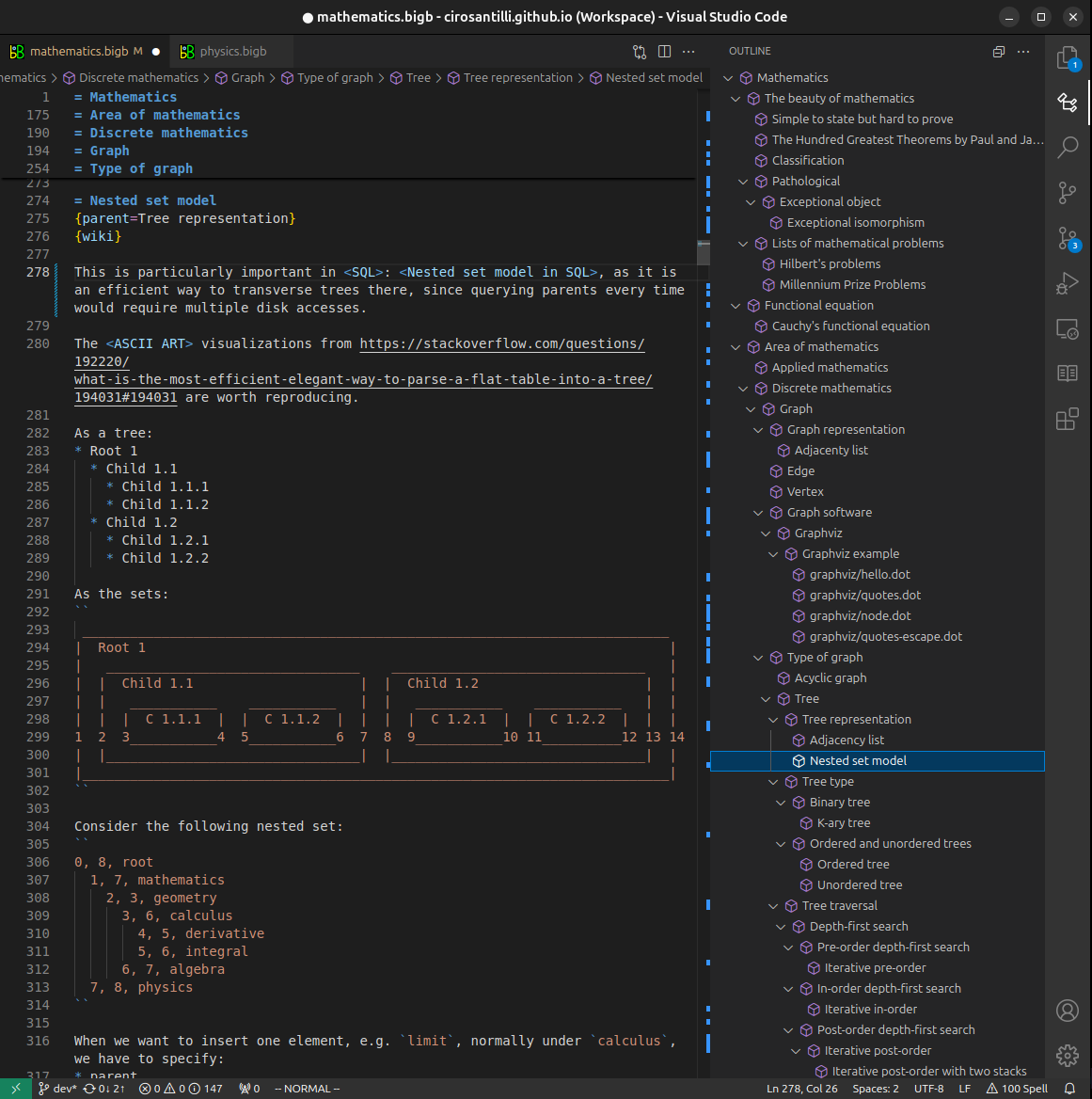

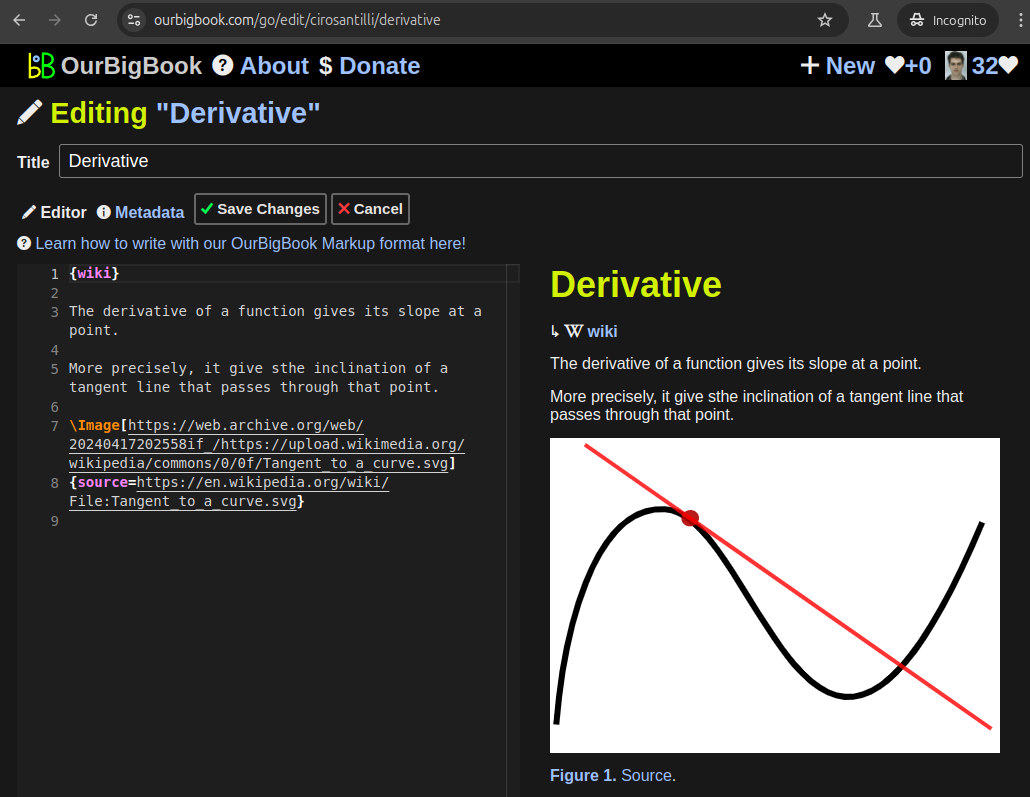

Figure 3. Visual Studio Code extension installation.Figure 4. Visual Studio Code extension tree navigation.Figure 5. Web editor. You can also edit articles on the Web editor without installing anything locally.Video 3. Edit locally and publish demo. Source. This shows editing OurBigBook Markup and publishing it using the Visual Studio Code extension.Video 4. OurBigBook Visual Studio Code extension editing and navigation demo. Source. - Infinitely deep tables of contents:

All our software is open source and hosted at: github.com/ourbigbook/ourbigbook

Further documentation can be found at: docs.ourbigbook.com

Feel free to reach our to us for any help or suggestions: docs.ourbigbook.com/#contact