SOGIN (Società Gestione Impianti Nucleari) is an Italian public company responsible for the management and decommissioning of nuclear facilities and the handling of radioactive waste in Italy. Established in 1999, SOGIN's primary mission is to ensure the safe and secure dismantling of nuclear power plants and the proper management of radioactive materials that result from this process. The company also works on waste management and disposal strategies, ensuring compliance with national and international safety standards.

As of my last knowledge update in October 2021, Japan had several nuclear power plants, but many of them were offline due to safety concerns and regulatory changes following the Fukushima Daiichi nuclear disaster in 2011. Below is a list of some of the major nuclear power plants in Japan: 1. **Kashiwazaki-Kariwa Nuclear Power Plant** (Niigata Prefecture) 2.

The T-15 reactor is a research nuclear reactor located in Russia, specifically at the Kurchatov Institute in Moscow. It is primarily used for scientific research and experiments in the field of nuclear physics, engineering, and materials science. The reactor is part of Russia's broader efforts in nuclear research and technology development. T-15 is characterized as a pool type reactor, utilizing low-enriched uranium fuel, and it is designed to facilitate various types of experiments.

Orano is a French multinational company that specializes in the nuclear industry, focusing on the entire nuclear fuel cycle. Established as a result of a reorganization of the nuclear activities of the publicly traded company Areva in 2016, Orano's primary activities include uranium extraction, conversion, enrichment, and recycling of nuclear materials.

Slovenia has one operational nuclear power station, the Krško Nuclear Power Plant (Nuklearna elektrarna Krško or NEK). Located near the town of Krško, it is the only nuclear facility in Slovenia and plays a significant role in the country's energy production.

The Korea Atomic Energy Research Institute (KAERI) is a prominent research institute in South Korea focused on nuclear science and technology. Established in 1959, KAERI plays a key role in advancing nuclear research, developing nuclear power technology, and promoting the peaceful use of nuclear energy.

The United Arab Emirates (UAE) has made significant investments in nuclear power as part of its strategy to diversify its energy sources and reduce reliance on fossil fuels. The primary nuclear power project in the UAE is the Barakah Nuclear Energy Plant. ### Barakah Nuclear Energy Plant: 1. **Location**: The Barakah Nuclear Energy Plant is situated in the Al Dhafra region of Abu Dhabi.

As of my last knowledge update in October 2023, there isn't widely recognized information about a businessman named Robin Jeffrey in prominent business circles. It's possible that he could be a figure in a specific industry or region that hasn't gained broad recognition. If you have more context or details about Robin Jeffrey or the specific business domain he is associated with, that would help in providing a more accurate response. Alternatively, it's also possible that he emerged in the business scene after my last update.

B&W mPower is a brand of portable power solutions developed by Bowers & Wilkins (B&W), known for its high-quality audio products. The mPower system generally refers to a line of products designed to provide reliable, mobile charging solutions for electronic devices. These products often include features like high-capacity batteries, multiple charging ports, and the ability to power or recharge a variety of devices on-the-go.

Title 10 of the Code of Federal Regulations (CFR) pertains to Energy and is primarily focused on the regulations of the Nuclear Regulatory Commission (NRC). This section includes rules related to the regulation of nuclear materials, the licensing of nuclear facilities, the safety and security of nuclear reactors, and the handling of radioactive waste. It establishes standards, procedures, and requirements for various aspects of nuclear energy management, including the oversight of nuclear power plants and the use and disposal of nuclear materials.

Nuclear power in Pennsylvania plays a significant role in the state's energy landscape. As of my last update in October 2023, Pennsylvania is one of the largest producers of nuclear energy in the United States. The state is home to five nuclear power plants, which contribute a substantial portion of its electricity generation—about 40% of the state's electricity comes from nuclear power.

ELEMASH Machine-Building Plant, also known as the ELEMASH plant, is a manufacturer primarily involved in the production of machinery and equipment for various industries, including defense, aerospace, and other specialized sectors. It is located in Russia and has a history dating back to the Soviet era, having been established to support the needs of the military and other industrial sectors. The plant specializes in manufacturing a range of products, including artillery systems, ammunition, and various mechanical components.

The Joint Institute for Nuclear Research (JINR) is an intergovernmental scientific research organization located in Dubna, Russia. Established in 1956, it serves as a collaborative center for various countries to conduct research in nuclear physics, particle physics, and related fields. JINR is known for its contributions to various areas of research, including nuclear science, astrophysics, condensed matter physics, and medical physics.

Krasnaya Zvezda State Enterprise, also known as the Red Star Factory, is a prominent Russian company involved in the production of military and defense-related goods. Established in the Soviet era, it has been a significant player in the manufacturing of uniforms, equipment, and other materials for the military. The enterprise focuses on delivering high-quality products and has been known for its innovative approaches in textiles and engineering within the defense sector.

The JL-3, also known as the DF-41 (Dong Feng-41), is a Chinese intercontinental ballistic missile (ICBM) developed by China. It is part of China’s strategic nuclear deterrent forces and is designed to deliver multiple nuclear warheads over long distances, with an estimated range of about 12,000 kilometers (approximately 7,500 miles). This missile is capable of reaching targets in the continental United States.

Sortir du nucléaire (SDN) is a French non-governmental organization founded in 1997 that advocates for the phase-out of nuclear energy in France. The organization's name translates to "Get Out of Nuclear" in English. SDN aims to promote sustainable energy solutions and raise public awareness about the risks and drawbacks associated with nuclear power, including safety concerns, waste management issues, and the environmental impact of nuclear energy.

The Redoutable-class submarines are a class of nuclear-powered ballistic missile submarines (SSBNs) that were built for the French Navy. They were designed and constructed in the 1960s, with the lead vessel, the FS Redoutable (S611), being commissioned in 1971. The class is significant as it represented France's entry into the field of nuclear deterrence during the Cold War.

The Pierre-sur-Haute military radio station is a significant telecommunications facility operated by the French military. Located in the Auvergne region, specifically on the summit of Pierre-sur-Haute in the Forez mountains, it plays a crucial role in military communications. Established during the Cold War, the station is designed to support secure radio communication for the French armed forces and contributes to their operational capabilities. The site is strategically positioned to provide extensive coverage and is equipped with various antennas and communication systems.

Barbara Lochbihler is a German politician and a member of the Green Party (Die Grünen). She has been involved in various political roles and has served in the European Parliament. Lochbihler is known for her focus on human rights, environmental issues, and international relations.

Helmuth Prieß is best known as a German fishery biologist and environmentalist, particularly noted for his research and contributions to the understanding of aquatic ecosystems and sustainable fishing practices. His work often focuses on the balance between fish populations and their environments, promoting the importance of conservation and sustainable practices within the fishing industry.

Pinned article: Introduction to the OurBigBook Project

Welcome to the OurBigBook Project! Our goal is to create the perfect publishing platform for STEM subjects, and get university-level students to write the best free STEM tutorials ever.

Everyone is welcome to create an account and play with the site: ourbigbook.com/go/register. We belive that students themselves can write amazing tutorials, but teachers are welcome too. You can write about anything you want, it doesn't have to be STEM or even educational. Silly test content is very welcome and you won't be penalized in any way. Just keep it legal!

Intro to OurBigBook

. Source. We have two killer features:

- topics: topics group articles by different users with the same title, e.g. here is the topic for the "Fundamental Theorem of Calculus" ourbigbook.com/go/topic/fundamental-theorem-of-calculusArticles of different users are sorted by upvote within each article page. This feature is a bit like:

- a Wikipedia where each user can have their own version of each article

- a Q&A website like Stack Overflow, where multiple people can give their views on a given topic, and the best ones are sorted by upvote. Except you don't need to wait for someone to ask first, and any topic goes, no matter how narrow or broad

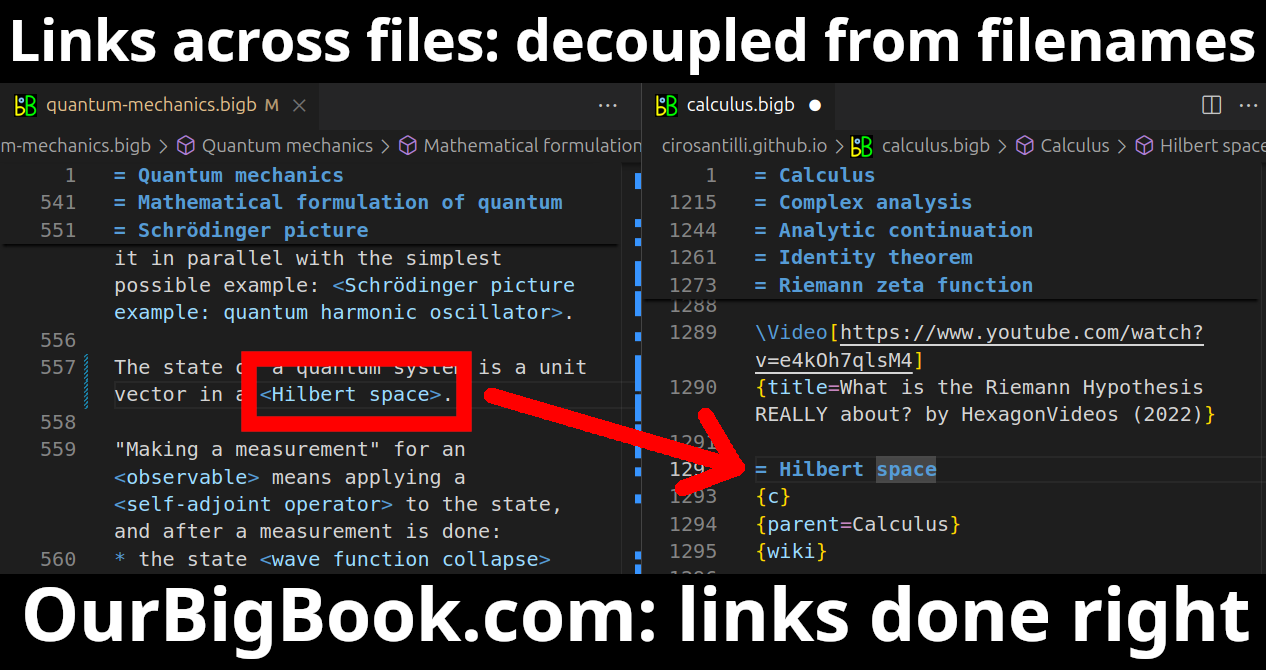

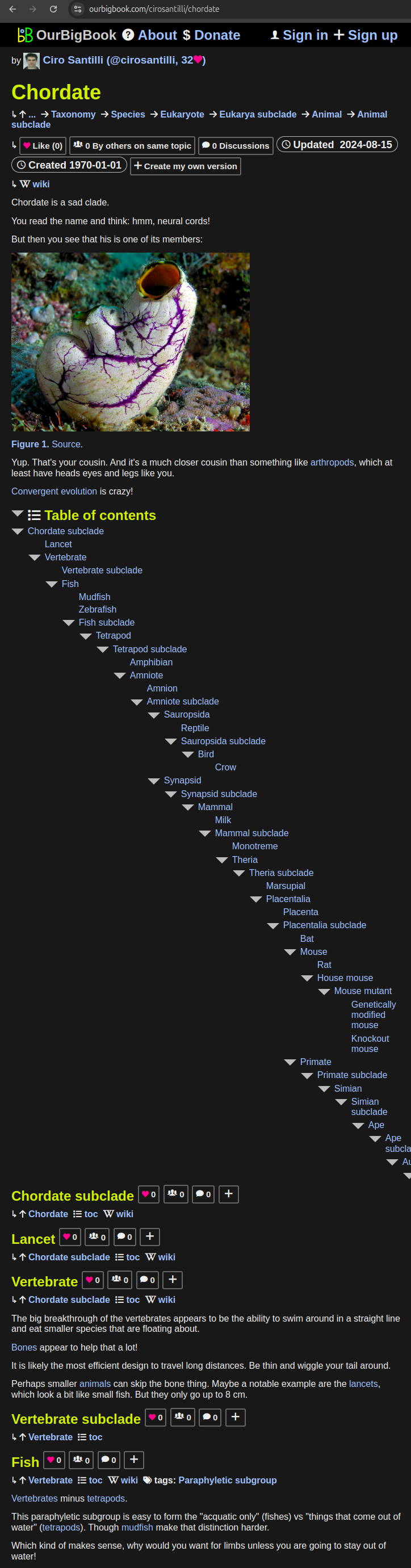

This feature makes it possible for readers to find better explanations of any topic created by other writers. And it allows writers to create an explanation in a place that readers might actually find it.Figure 1. Screenshot of the "Derivative" topic page. View it live at: ourbigbook.com/go/topic/derivativeVideo 2. OurBigBook Web topics demo. Source. - local editing: you can store all your personal knowledge base content locally in a plaintext markup format that can be edited locally and published either:This way you can be sure that even if OurBigBook.com were to go down one day (which we have no plans to do as it is quite cheap to host!), your content will still be perfectly readable as a static site.

- to OurBigBook.com to get awesome multi-user features like topics and likes

- as HTML files to a static website, which you can host yourself for free on many external providers like GitHub Pages, and remain in full control

Figure 3. Visual Studio Code extension installation.Figure 4. Visual Studio Code extension tree navigation.Figure 5. Web editor. You can also edit articles on the Web editor without installing anything locally.Video 3. Edit locally and publish demo. Source. This shows editing OurBigBook Markup and publishing it using the Visual Studio Code extension.Video 4. OurBigBook Visual Studio Code extension editing and navigation demo. Source. - Infinitely deep tables of contents:

All our software is open source and hosted at: github.com/ourbigbook/ourbigbook

Further documentation can be found at: docs.ourbigbook.com

Feel free to reach our to us for any help or suggestions: docs.ourbigbook.com/#contact