The number 17 is a natural number that follows 16 and precedes 18. It is an odd prime number, meaning it has no positive divisors other than 1 and itself. In various contexts, 17 can represent different things, such as: 1. **Mathematics**: Its properties include being a prime number, the sum of the first four prime numbers (2 + 3 + 5 + 7), and part of various mathematical sequences.

The 143rd meridian east is a line of longitude located 143 degrees east of the Prime Meridian, which is located at 0 degrees longitude. This meridian runs from the North Pole to the South Pole, crossing through various countries and territories in the eastern hemisphere. In terms of geography, the 143rd meridian east passes through parts of the following areas: - **Australia**: It crosses through the northeastern part of Australia, including regions in Queensland.

The 146th meridian west is a line of longitude that is 146 degrees west of the Prime Meridian, which is located at 0 degrees longitude. This meridian runs from the North Pole to the South Pole, crossing various regions along the way. In the northern hemisphere, the 146th meridian west passes through parts of Alaska and the Aleutian Islands. In the southern hemisphere, it crosses through the South Pacific Ocean.

The 151st meridian east is a line of longitude that is 151 degrees east of the Prime Meridian, which is set at 0 degrees longitude. This meridian runs from the North Pole to the South Pole, passing through various regions along the way. Notable areas that the 151st meridian east passes through include parts of the Pacific Ocean, as well as islands such as New Zealand and various territories in the South Pacific.

The 159th meridian east is a line of longitude that is located 159 degrees east of the Prime Meridian, which is defined as 0 degrees longitude. Like all lines of longitude, it runs from the North Pole to the South Pole. The 159th meridian east passes through the Pacific Ocean, and it is located east of countries such as Russia's Kamchatka Peninsula and north of New Zealand.

The 171st meridian east is a line of longitude that is 171 degrees east of the Prime Meridian. It runs from the North Pole to the South Pole, passing through several regions.

Fuensanta Aroca might refer to a person, likely with notable contributions in a specific field, such as science, arts, or another area. However, based on the information I have up to October 2023, there isn't any widely recognized individual or entity by that name that is well-documented in public data. It could also refer to a specific location, event, or cultural reference that isn't extensively covered in major sources.

The 1978 Austrian nuclear power referendum was a significant event in Austria's political history regarding the decision on the future of nuclear energy in the country. The referendum took place on November 5, 1978, and was primarily focused on whether to continue the construction of a nuclear power plant in the town of Zwentendorf, which had already been partially built.

The 1998 bombing of Iraq primarily refers to a military operation conducted by the United States and the United Kingdom known as Operation Desert Fox. This operation took place from December 16 to December 19, 1998, and involved a series of airstrikes aimed at degrading Iraq's ability to produce and deploy weapons of mass destruction (WMDs).

"2001: A Space Odyssey" is a science fiction novel written by Arthur C. Clarke, originally published in 1968. The book was developed as a companion piece to Stanley Kubrick's film of the same name, which was released in the same year. However, Clarke's novel and the film evolved separately, with their respective stories and themes expanding on the same overarching concepts.

The term "2013 Nordic storms" generally refers to a series of severe weather events that affected the Nordic countries (Denmark, Finland, Iceland, Norway, and Sweden) during the winter of 2013. These storms were characterized by heavy snowfall, strong winds, and significant disruptions to transportation and daily life across the region. One of the most notable storms during this period was Storm "Hilde," which caused widespread damage and power outages in several areas.

In 2014, North Korea conducted a series of missile tests that raised significant international concern and condemnation. Throughout the year, the country launched various short-range and medium-range ballistic missiles, as well as other types of projectiles, demonstrating advancements in its missile capabilities. Key aspects of the 2014 missile tests include: 1. **Frequency of Tests**: North Korea conducted multiple missile launches during the year, particularly in the first half of 2014.

The number 202 is an integer that comes after 201 and before 203. In terms of its properties: - It is an even number. - It is a composite number, meaning it has divisors other than 1 and itself (the divisors of 202 are 1, 2, 101, and 202). - In Roman numerals, 202 is represented as CCII. - In binary, it is written as 11001010.

The 20th century saw significant contributions to mathematics from various Greek mathematicians, who made notable impacts in fields such as algebra, analysis, geometry, and number theory. Here are some prominent Greek mathematicians from that era: 1. **Constantin Carathéodory (1861–1950)** - A mathematician who made contributions in various areas including measure theory, the calculus of variations, and thermodynamics. He also worked on the theory of functions of a complex variable.

The 20th century saw several significant Latvian mathematicians who made contributions to various fields of mathematics. Here are a few notable figures: 1. **Gustavs E. M. M. (Gustavs) Hermannis (1914–1985)**: Hermannis made contributions in the field of geometry. He worked on various aspects of topology and had an interest in the foundations of mathematics.

Anupam Mazumdar is a prominent astrophysicist and cosmologist known for his research in the fields of theoretical cosmology and astrophysics. He has made significant contributions to understanding the early universe, including cosmic inflation and dark energy. His work often involves applying mathematical models to describe the universe's structure and evolution. You may be referring to research papers, academic collaborations, or other specific aspects of his work.

Artificial intelligence (AI) has a wide range of applications across various industries and domains. Here are some key applications: 1. **Healthcare**: - **Medical Diagnosis**: AI algorithms analyze medical images (e.g., X-rays, MRIs) to detect diseases like cancer. - **Personalized Medicine**: AI helps in tailoring treatments based on individual patient data. - **Drug Discovery**: AI accelerates the research and development of new drugs by predicting molecular interactions.

Pinned article: Introduction to the OurBigBook Project

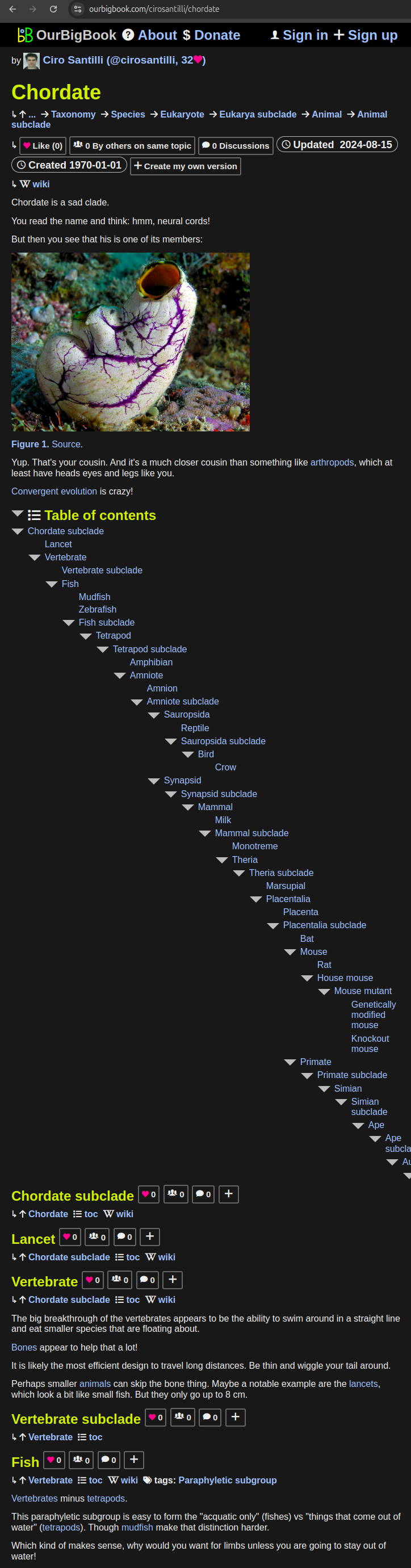

Welcome to the OurBigBook Project! Our goal is to create the perfect publishing platform for STEM subjects, and get university-level students to write the best free STEM tutorials ever.

Everyone is welcome to create an account and play with the site: ourbigbook.com/go/register. We belive that students themselves can write amazing tutorials, but teachers are welcome too. You can write about anything you want, it doesn't have to be STEM or even educational. Silly test content is very welcome and you won't be penalized in any way. Just keep it legal!

Intro to OurBigBook

. Source. We have two killer features:

- topics: topics group articles by different users with the same title, e.g. here is the topic for the "Fundamental Theorem of Calculus" ourbigbook.com/go/topic/fundamental-theorem-of-calculusArticles of different users are sorted by upvote within each article page. This feature is a bit like:

- a Wikipedia where each user can have their own version of each article

- a Q&A website like Stack Overflow, where multiple people can give their views on a given topic, and the best ones are sorted by upvote. Except you don't need to wait for someone to ask first, and any topic goes, no matter how narrow or broad

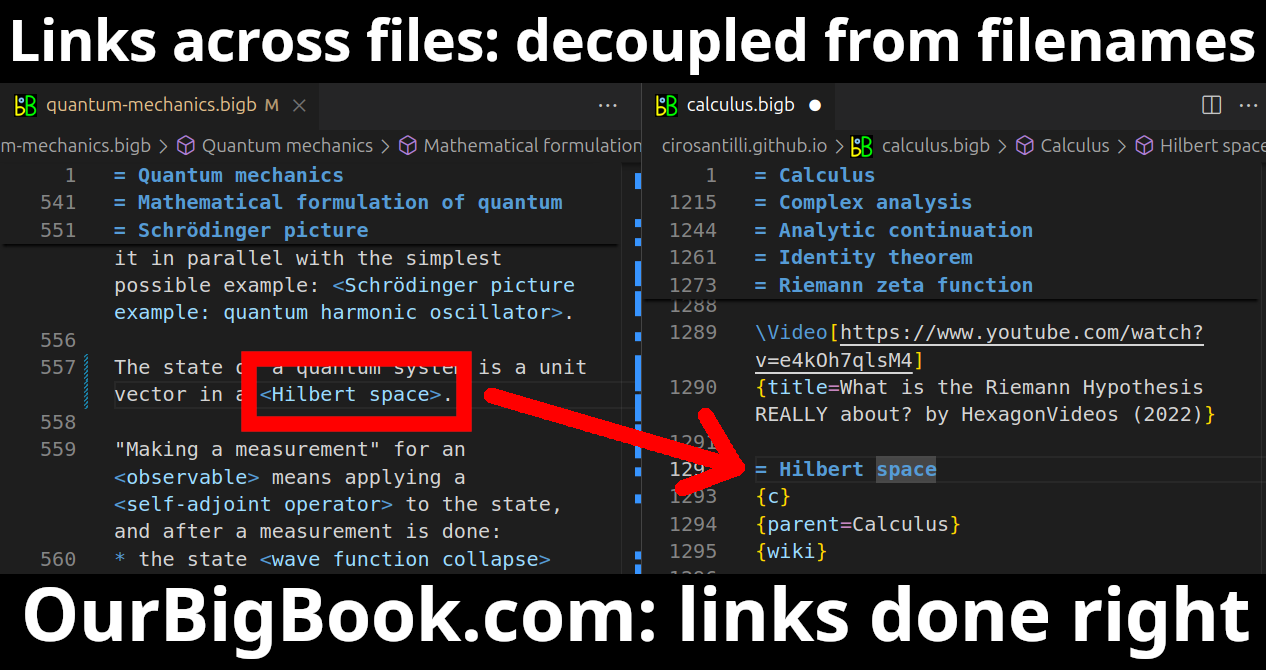

This feature makes it possible for readers to find better explanations of any topic created by other writers. And it allows writers to create an explanation in a place that readers might actually find it.Figure 1. Screenshot of the "Derivative" topic page. View it live at: ourbigbook.com/go/topic/derivativeVideo 2. OurBigBook Web topics demo. Source. - local editing: you can store all your personal knowledge base content locally in a plaintext markup format that can be edited locally and published either:This way you can be sure that even if OurBigBook.com were to go down one day (which we have no plans to do as it is quite cheap to host!), your content will still be perfectly readable as a static site.

- to OurBigBook.com to get awesome multi-user features like topics and likes

- as HTML files to a static website, which you can host yourself for free on many external providers like GitHub Pages, and remain in full control

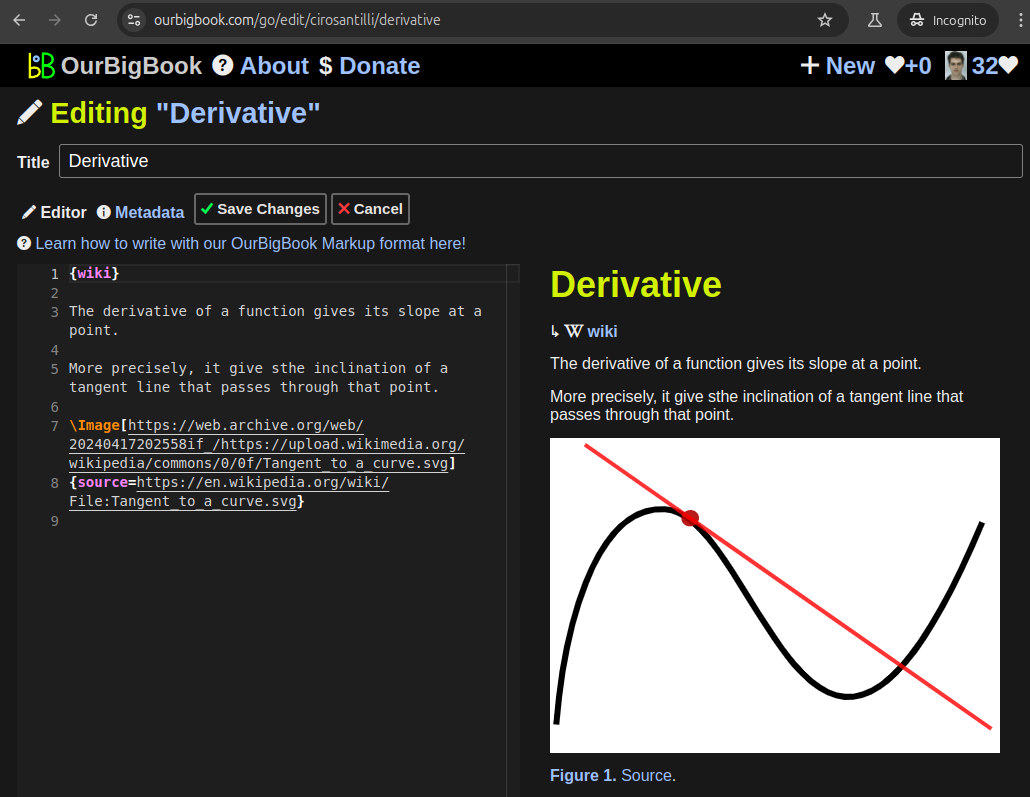

Figure 3. Visual Studio Code extension installation.Figure 4. Visual Studio Code extension tree navigation.Figure 5. Web editor. You can also edit articles on the Web editor without installing anything locally.Video 3. Edit locally and publish demo. Source. This shows editing OurBigBook Markup and publishing it using the Visual Studio Code extension.Video 4. OurBigBook Visual Studio Code extension editing and navigation demo. Source. - Infinitely deep tables of contents:

All our software is open source and hosted at: github.com/ourbigbook/ourbigbook

Further documentation can be found at: docs.ourbigbook.com

Feel free to reach our to us for any help or suggestions: docs.ourbigbook.com/#contact